# WSM: Characterization of transistor drain supply terminal impedance at signal envelope frequencies

Zoya Popovic, Scott Schafer,

David Sardin, Tibault Reveyrand \*

University of Colorado, Boulder

\*XLIM, Limoges, France

WMC: The Importance of Low-frequency Measurements on High-frequency Characterization

#### **Outline and Topics**

- Some applications that require low-frequency characterization of microwave components or devices

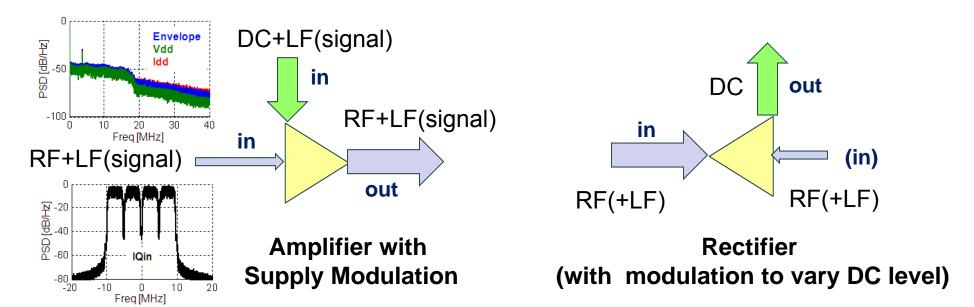

- Supply modulated PAs and drain supply characterization

- "Time reversal" of PAs transistor rectifier characterization

- What has not been done but would be useful

#### Bias and signals

- Applications:

- > Efficient power amplifications of increasingly difficult signals

- Wireless powering, power beaming, fast dc-dc conversion

- Supply dynamically modulated at signal (LF) bandwidth to improve PA efficiency requires modeling at very different time scales

- Modulating a RF powering signal allows for improved conversion efficiency or variable DC power level

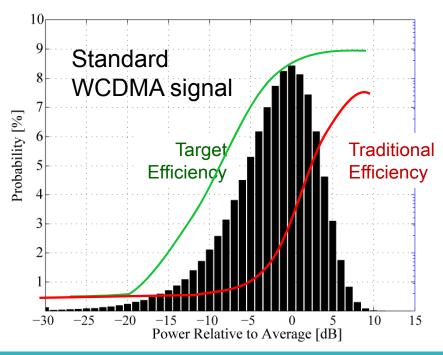

## Motivation: high efficiency for high PAR signals

- PA consumes most power

- 1.4W required for cooling, power distribution, etc, for each 1W dissipated

- Traditional high-PAR PA efficiency

- Efficiency degrades with reduced output power

- Average efficiency is low for high-PAR signals

- Techniques in this work

- Raise PA efficiency at PEP with harmonic-tuned PA design to >80%

- Extend high-efficiency PA operation to average power level

|                                           | 30%<br>Efficiency | 50%<br>Efficiency |

|-------------------------------------------|-------------------|-------------------|

| RF Output Power                           | 50W               | 50W               |

| Dissipated in PA                          | 117W              | 50W               |

| Dissipated by cooling, distribution, etc. | 165W              | 71W               |

| Total Input Power                         | 332W              | 171W              |

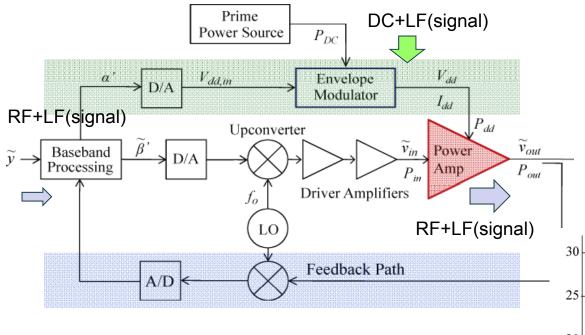

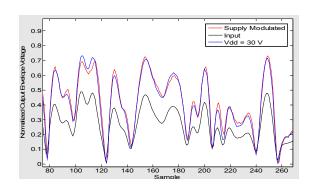

#### **Supply-modulated PAs**

- Most of the envelope modulates the supply

- A portion of the envelope modulates the drive

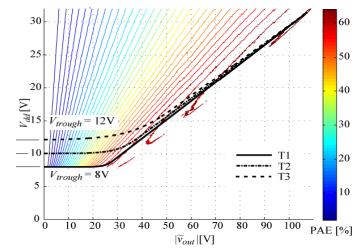

- The trajectory optimizes efficiency

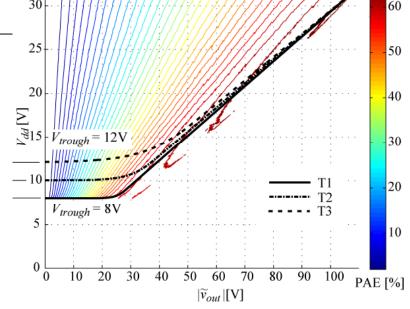

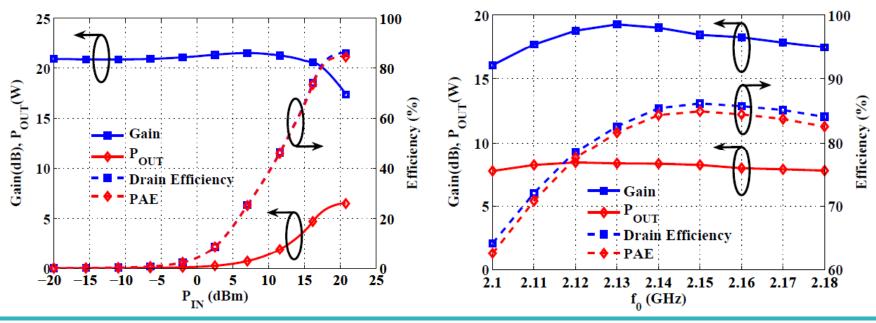

- Measured GaN PA at 2.14GHz

- Three example trajectories perform tradeoff between PA efficiency and supply modulator requirements

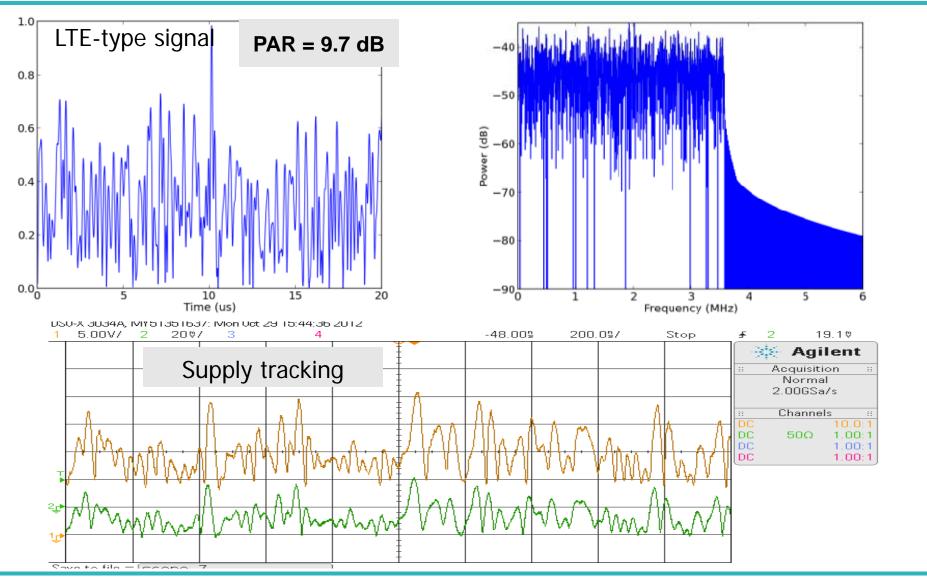

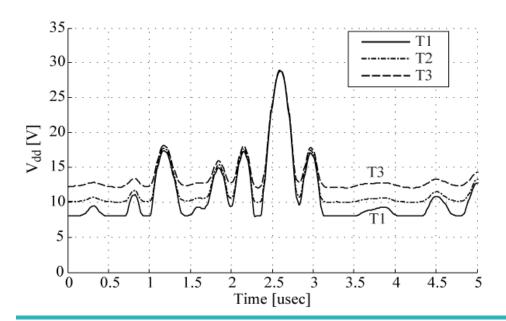

#### **Example low-bandwidth high PAR signal**

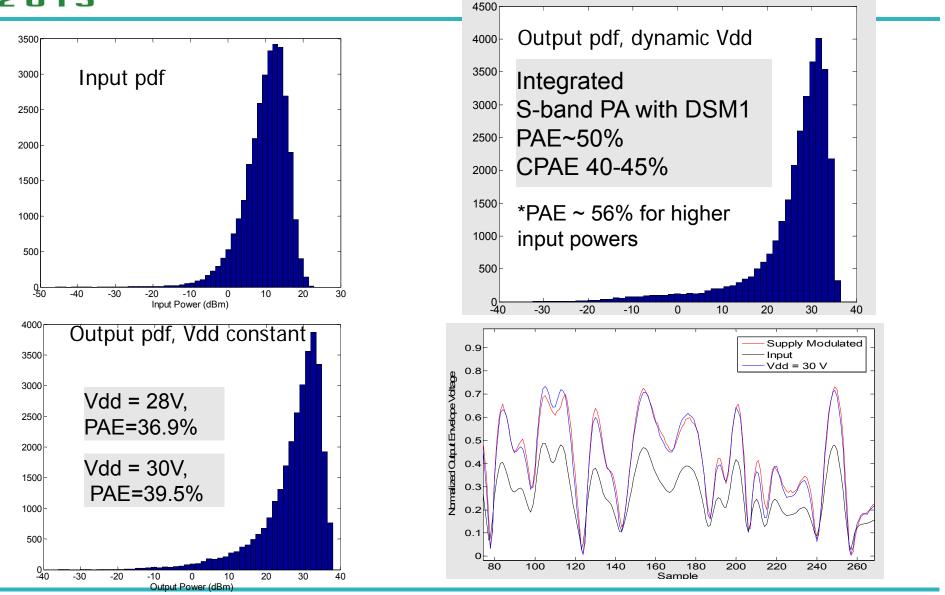

#### Result with high efficiency supply modulator

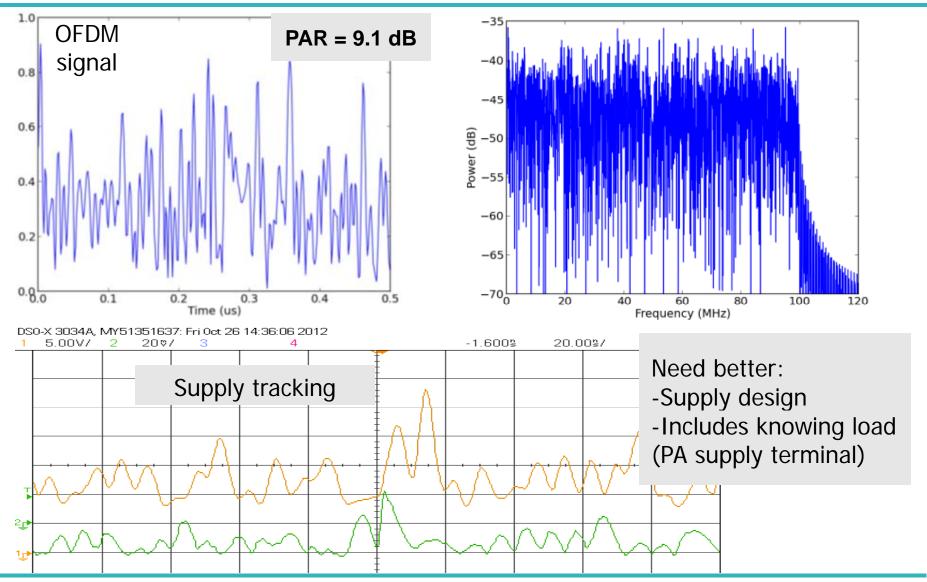

#### Increased bandwidth high PAR signal

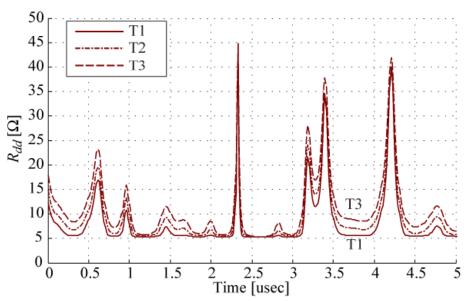

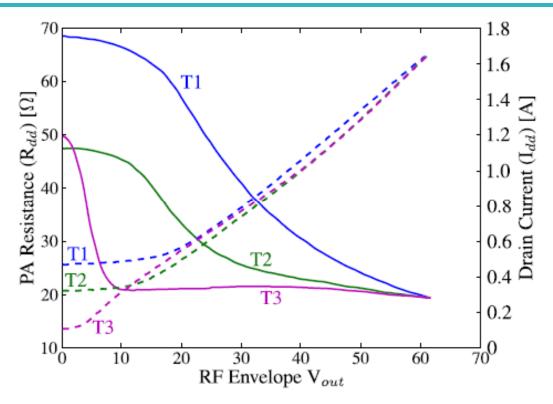

#### **Dynamic resistance**

- Trajectory T1 clearly has amore dynamic drain impedance than T3

- Can we quantify and how does it impact PA design?

$$R_{dd} = \frac{V_{dd}^2 \eta_d}{P_{out}}$$

#### Simulated drain resistance

$$R_{dd} = V_{supply}/I_{supply}$$

$$R_{dd} = V_{supply}^2 \cdot \eta_d / P_{out}$$

At higher bandwidth, cannot be assumed to be purely real

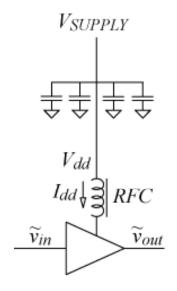

- R<sub>dd</sub> not directly related to PA load line; made constant over RF cycle by RFC

- the output impedance of the SM should be kept low over a wide frequency range to limit V<sub>supply</sub> error due to voltage division between the supply modulator output impedance and load PA impedance

- R<sub>dd</sub> and I<sub>dd</sub> both vary a lot more for T3 than for T2

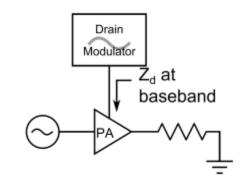

#### PA dynamic impedance measurement

- Bias tee is no longer a DC path

- Can the bias tee and output of the PA be optimized for drain modulation?

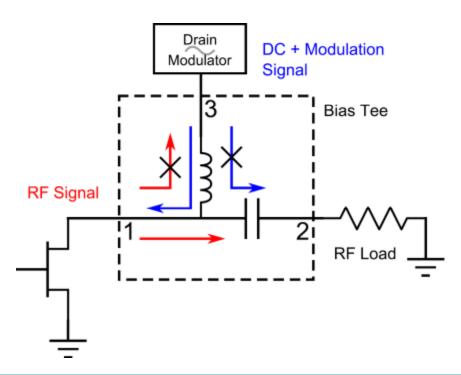

- Purpose of the drain bias tee is to direct the modulation signal to the transistor

- Desired bias tee S-parameters:

$$S(f_{BB}, f_{RF}) = \begin{bmatrix} 0, 0 & 0, 1 & 1, 0 \\ 0, 1 & 1, 0 & 0, 0 \\ 1, 0 & 0, 0 & 0, 1 \end{bmatrix}$$

### Complex drain impedance measurement

#### Traditional bias network

- Bypass caps

- Source large dynamic currents

- Reject ripple at high frequency

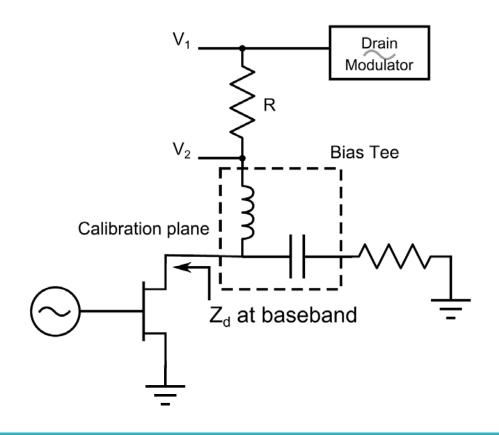

#### SMPA bias network

- EM+interconnect

- Low large-signal output impedance required over wide frequency range

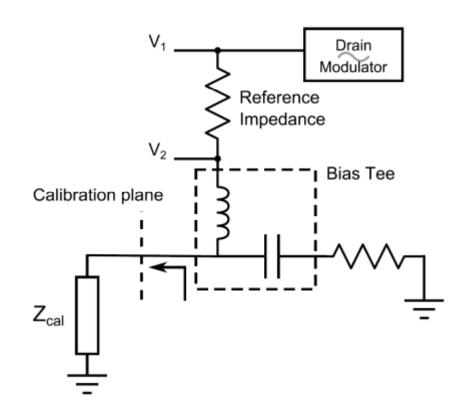

- Determine complex impedance by voltage waveforms with oscilloscope (V<sub>1</sub>, V<sub>2</sub>)

- Calibration allows measurement plane to be moved to transistor

### Calibration for drain impedance measurement

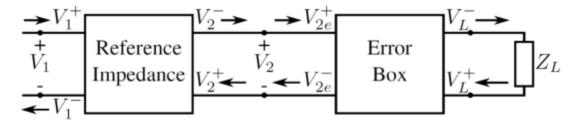

- A reflection coefficient (M<sub>A,B,C</sub>) can be found from the two complex voltages V<sub>1</sub>, V<sub>2</sub>

- Use 3 known standards A<sub>11</sub>, B<sub>11</sub>, C<sub>11</sub>

- Similar to Short-Open-Load calibration

- Can find S-parameters of Error Box [L]:

$$\begin{bmatrix} 1 & A_{11}M_A & -A_{11} \\ 1 & B_{11}M_B & -B_{11} \\ 1 & C_{11}M_C & -C_{11} \end{bmatrix} \begin{bmatrix} L_{11} \\ L_{22} \\ \Delta L \end{bmatrix} = \begin{bmatrix} M_A \\ M_B \\ M_C \end{bmatrix}$$

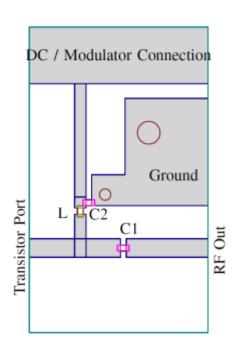

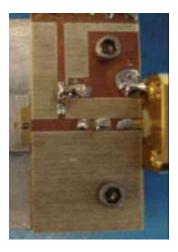

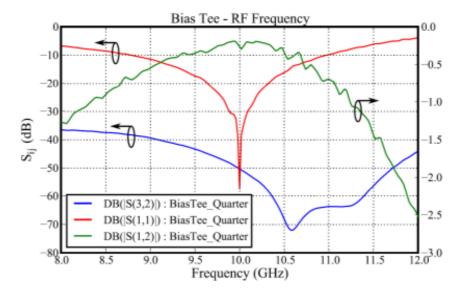

#### Design of a LF/RF bias Tee

- Simulated Bias Tee

- RF-Low Frequency Isolation > 30 dB

- 0.8 GHz RF match (-20 dB)

- Low frequency and RF through loss< 0.25 dB</li>

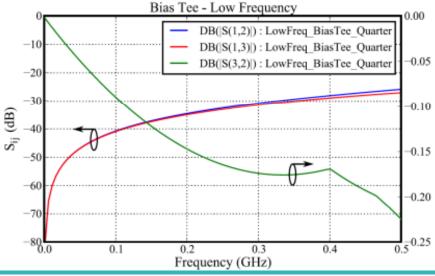

#### Drain impedance: calibration validation

- To verify the calibration and setup, a few arbitrary lumped impedances were measured

- Measuring

waveforms with low

amplitudes is difficult

(short, open)

- Accuracy of Z<sub>L</sub> ± 5%

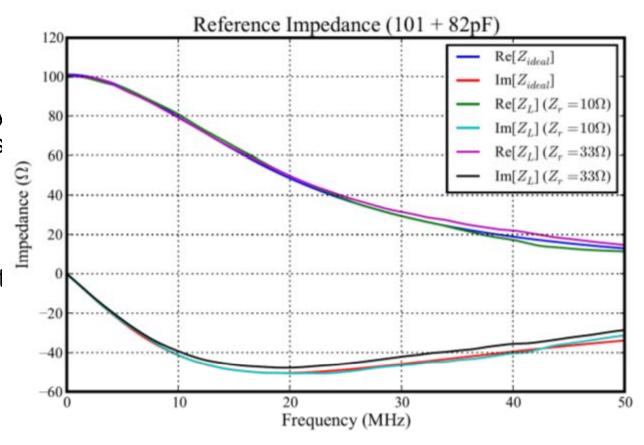

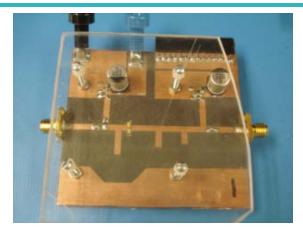

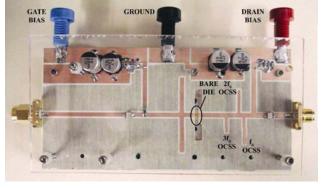

### Drain impedance measurements: transistor vs. PA, no RF drive

- Measurement setup is in progress

- Determine complex impedance by voltage waveforms with oscilloscope (V<sub>1</sub>, V<sub>2</sub>)

- Calibration allows measurement plane to be moved to transistor

(Measurements taken on different devices biased with a similar drain current. No RF power was applied.)

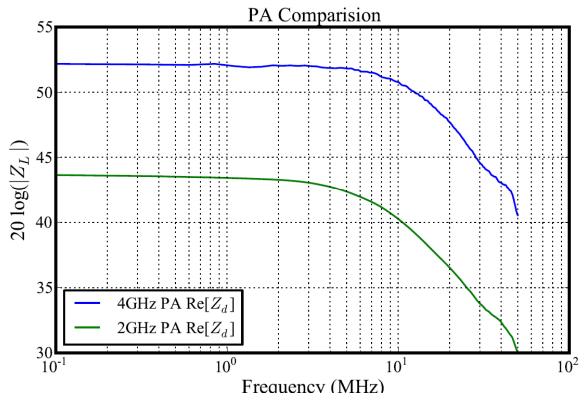

#### Difference between PAs

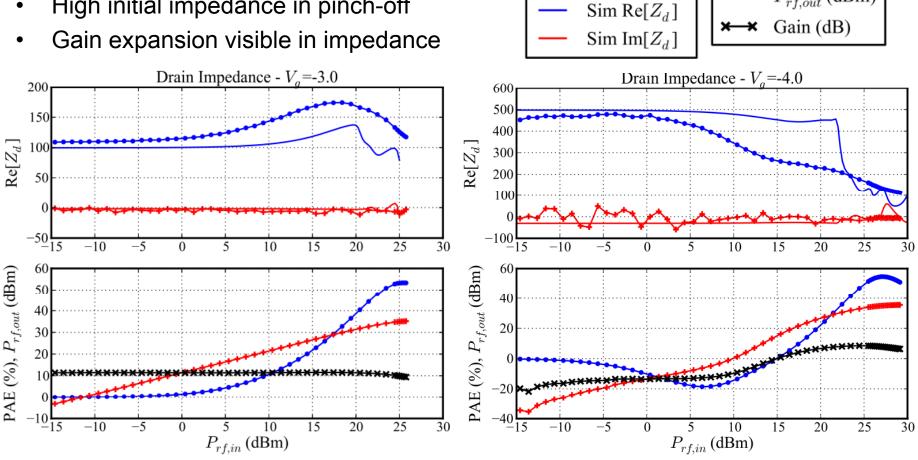

#### 4-GHz PA

- $I_d = 50 \text{ mA}$

- $V_{dpk-pk} = 5 V$

- $P_{in} = 15 \text{ dBm}$

#### 2-GHz PA

- $I_d = 160 \text{ mA}$

- $V_{dpk-pk} = 5 V$

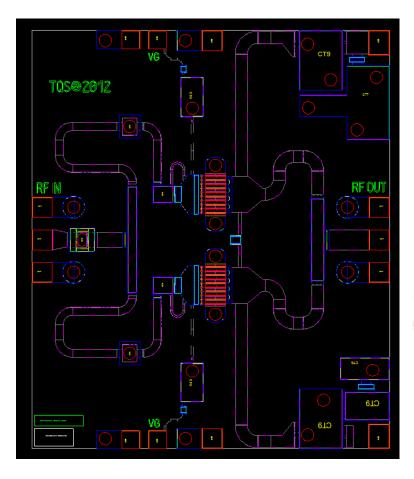

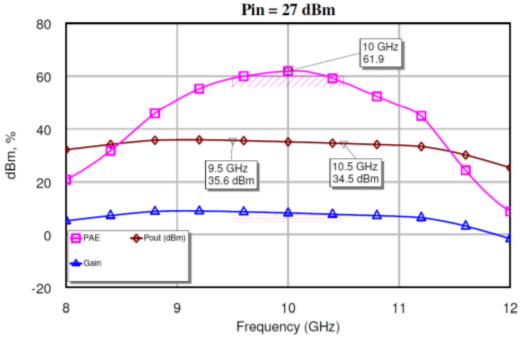

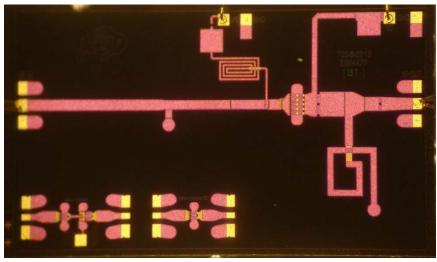

#### X-band GaN MMIC PA

Single stage PA, two devices combined with a reactive combiner, devices are 10 fingers x100um

Total die size: 2.0mmx2.3mm TriQuint 0.15um GaN process

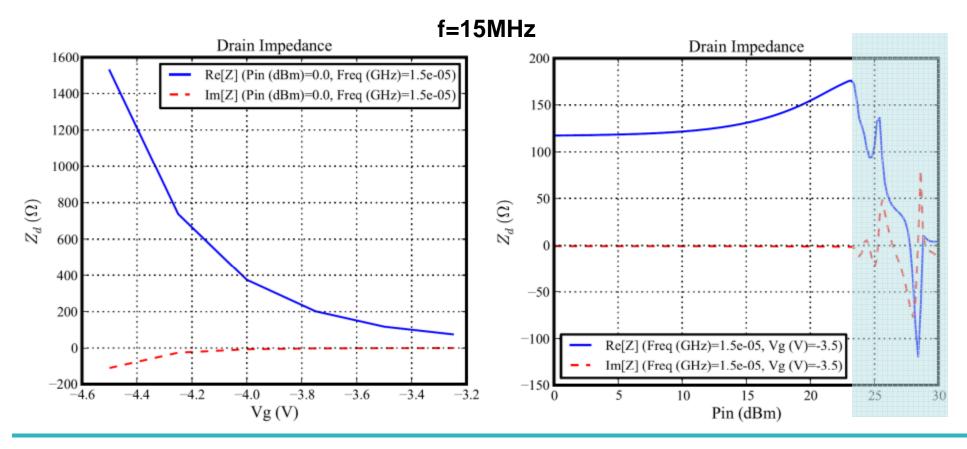

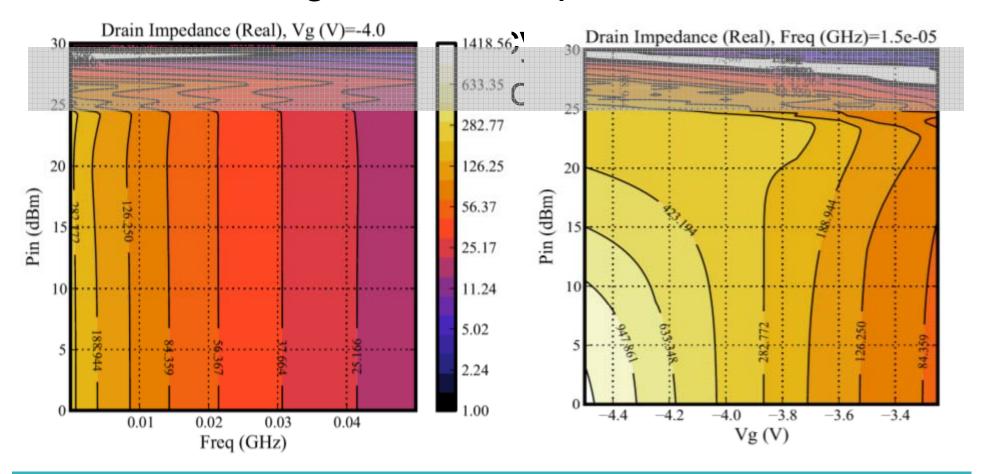

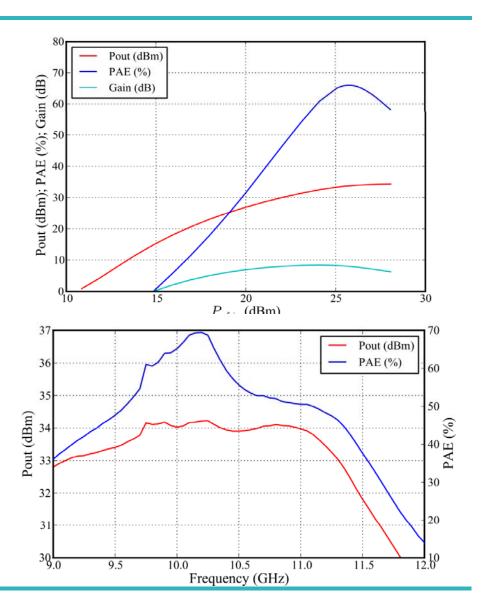

#### **Drain Impedance Simulations**

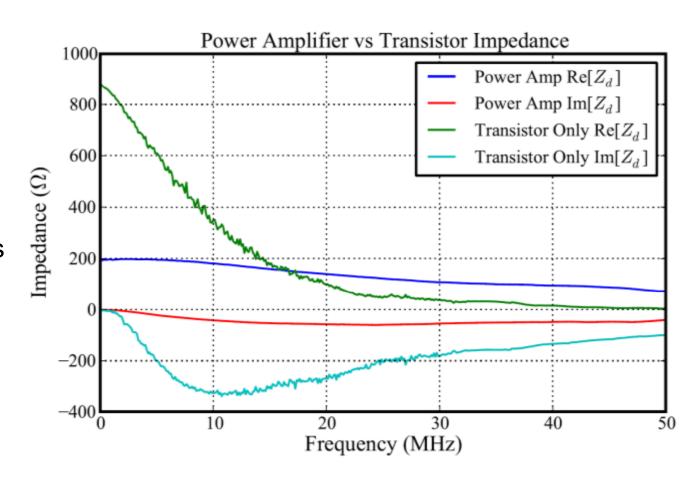

- Increasing bias decreases real and imaginary impedance (pinchoff to active)

- Increasing input power increases real impedance until saturation

#### **Drain Impedance Simulations**

While regions near top at high input power indicate negative real impedance

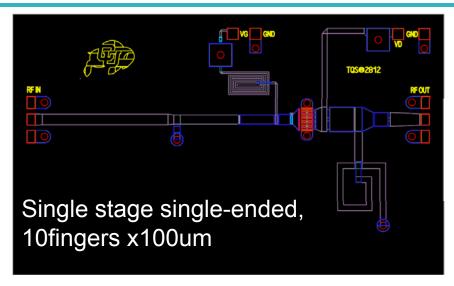

#### Single-ended X-band MMIC PA

3.8mmx2.3mm

#### MMIC PA drain impedance measurements

- Impedance increases before saturation

- Imaginary impedance approximately  $0\Omega$

- High initial impedance in pinch-off

f = 5 MHz

PAE (%)

$P_{rf,out}$  (dBm)

Meas Re[ $Z_d$ ]

Meas  $Im[Z_d]$

## Conclusions about drain impedance measurements

- Variation of impedance at high modulation frequency is not negligible

- Requires accurate characterization of transistor or accurate modeling.

- Accuracy of model at low frequencies with output saturation is debatable

- Calibration at low frequency is critical

- Good measured results and correlation with nonlinear device model can help design PA for SM/ET

- A linear very broadband supply modulator might be the best way to measure the dynamic drain impedance

- A low-frequency network analyzer is also an option

#### **Supply issues:**

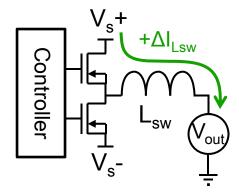

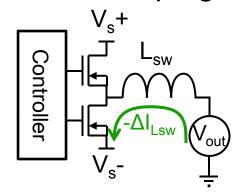

#### **Current Slew-Rate in an SMPS**

#### Current Ramping Up

$$\frac{\Delta I_{Lsw}}{\Delta t} = \frac{V_S^+ - V_{out}}{L_{sw}}$$

#### **Current Ramping Down**

$$\frac{\Delta I_{Lsw}}{\Delta t} = \frac{V_{out} - V_S^{-}}{L_{sw}}$$

#### Slew rate determined by:

- inductance L<sub>sw</sub>

- positive V<sub>s</sub><sup>+</sup> and negative V<sub>s</sub><sup>-</sup> DC supply rails

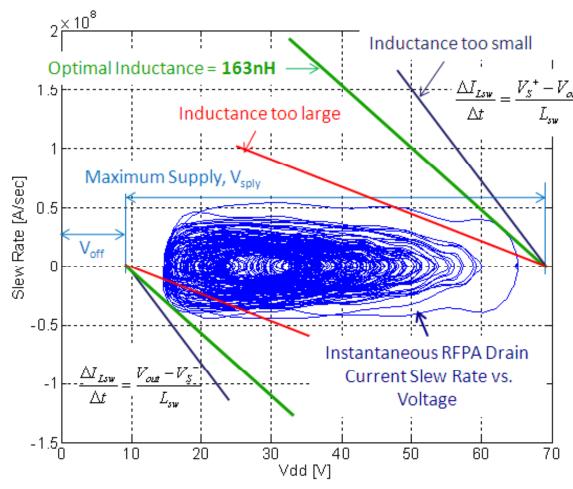

## Connection between SM and PA important

- For a given envelope waveform, required current slew rate is shown as a function of drain supply voltage

- V<sub>s</sub><sup>+</sup> , V<sub>s</sub><sup>-</sup> and the largest inductance L<sub>sw</sub> that meets the worst-case slew-rate requirement

- Example: 2-carrier

WCDMA, 6.8 dB PAR,

200W peak, 65V RFPA

$L_{sw}$  = very small for high slew rate operation

#### Conclusions about SMPA lowfrequency measurements

- Low-frequency important at input/output, but that can be characterized at baseband

- Non-standard measurements needed to characterize dynamic supply port impedance

- Good measurements and ultimate correlation with (new) models will allow for improved PA/SM co-design

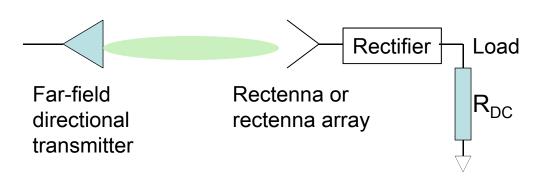

## Motivation for rectifier measurements

#### Wireless power beaming

- Wireless beaming vs. harvesting

- Modulate RF with LF to improve rectification efficiency

- Schottky diodes cannot handle high power

- Use transistors as rectifiers

#### Fast switching dc-dc converters

- Wireless beaming vs. harvesting

- Modulate RF with LF to improve rectification efficiency

- Schottky diodes cannot handle high power

- · Use transistors as rectifiers

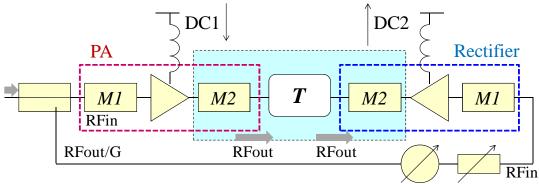

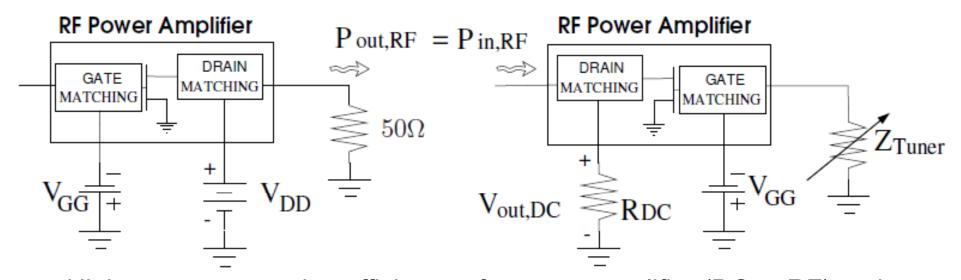

#### **Rectifier-PA duality**

High power conversion efficiency of a power amplifier (DC to RF) and a rectifier obtained by operating the amplifier in reverse (RF to DC) is achieved with time-reversal duality of the transistor's main current source. The power amplifier (PA) and rectifier (R) drain terminal voltage and current are related by

$$v_{PA}(t) = v_R(t)$$

$i_{PA}(t) = -i_R(t)$

Hamill, D.C.: 'Time Reversal Duality and the synthesis of a double class E DC-DC converter', 21st Annual IEEE Power Electronics Specialists Conference, 1990, pp. 512-521

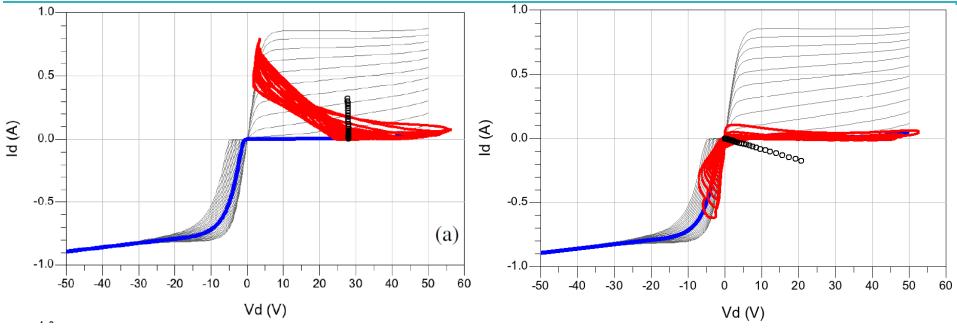

#### **Class-F PA and Rectifier Simulations**

- Simulations performed with a 8x75um GaN HEMT model at 2.14GHz

- The nonlinear model includes:

- Nonlinear Cgs, Cgd, Cds

- Gate-source and gate-drain diodes

- Breakdown modeling

- Trapping effect modeling

- Model reproduces nonlinear behavior for positive and negative drain voltages

- For PA, consider drain efficiency as metric

$$\eta_{PA} = \frac{P_{out,RF}}{P_{DC}}$$

- In class-F, 5 harmonics terminated

- Vds=28V, Vgs=-4.9V, obtained efficiency of 72%

- Observe I-V curves and load-line, and V,I waveforms and compare to rectifier

Callet, G., Faraj, J., Jardel, O., Charbonniaud, C., Jacquet, J.C., Reveyrand, T., Morvan, E., Piotrowicz, S., Teyssier, J.P. and Quéré R.: 'A new nonlinear HEMT model for AlGaN/GaN switch applications', Intern. Journal of Microwave and Wireless Techn., 2010, 2, (3-4), pp. 283-291

#### **Class-F PA and Rectifier Simulations**

- Simulations performed for rectifier mode with the same 8x75um GaN HEMT model at 2.14GHz

- Drain supply replaced by Rdc

- The input is now RF power P<sub>inRF</sub>=P<sub>outRF</sub> of the amplifier, injected in drain port

- Assuming DC gate current is negligible, the RF-DC conversion efficiency given by

$$\eta_R = \frac{P_{DC}}{P_{in,RF}} = \frac{2|V_{DC}|^2}{R_{DC} \Re\{V_{drain}(f_0)I_{drain}^*(f_0)\}}$$

- In class-F, 5 harmonics terminated

- Pin=, Vgs=-4.9V, obtained efficiency of 80% with Rdc=120 $\Omega$

- Observe I-V curves and load-line, and V,I waveforms and compare to rectifier

#### PA-rectifier time reversal

Simulated GaN transistor I-V curves (gray), dynamic load lines (red) and drain DC voltage and current (black) for the PA

The blue line is the Vgs=-4.9V transistor characteristic (the gate bias point value)

Vdd=28V, Power swept from 0-40dBm

Simulated GaN transistor I-V curves (gray), dynamic load lines (red) and drain DC voltage and current (black) for the rectifier

The blue line is the Vgs=-4.9V transistor characteristic (the gate bias point value) Time-reversal duality is seen at 2.14 GHz.

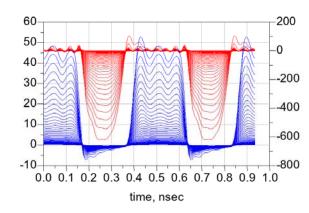

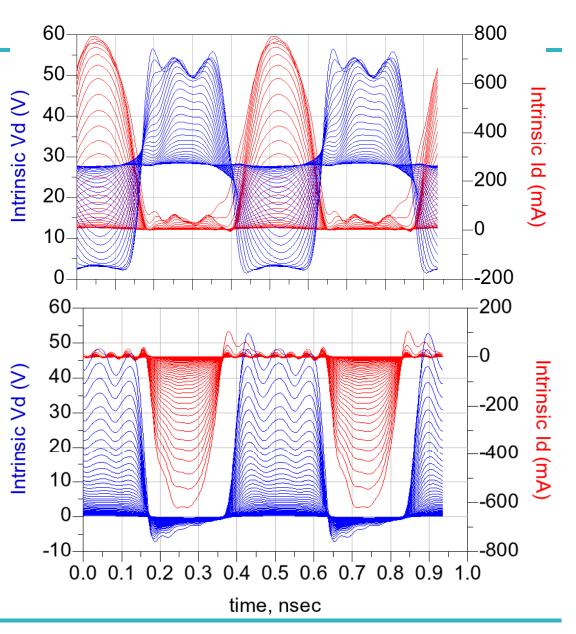

#### Simulated time domain waveforms

Simulated GaN transistor time domain intrinsic drain voltage (blue) and current for the power amplifier with Vds=28V, as the output power is swept from 0-40dBm

Simulated GaN transistor time domain intrinsic drain voltage (blue) and current for the rectifier as the power is swept from 0-40dBm

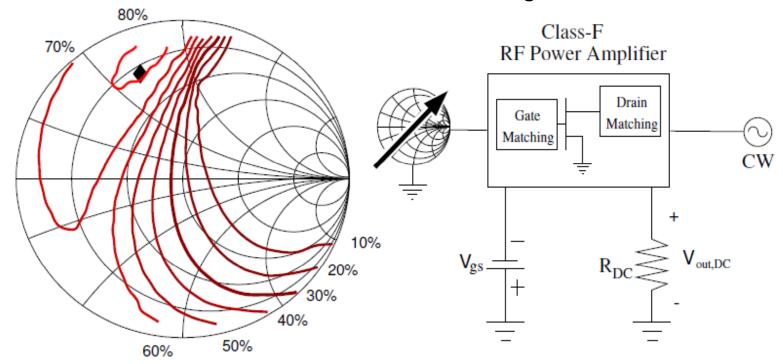

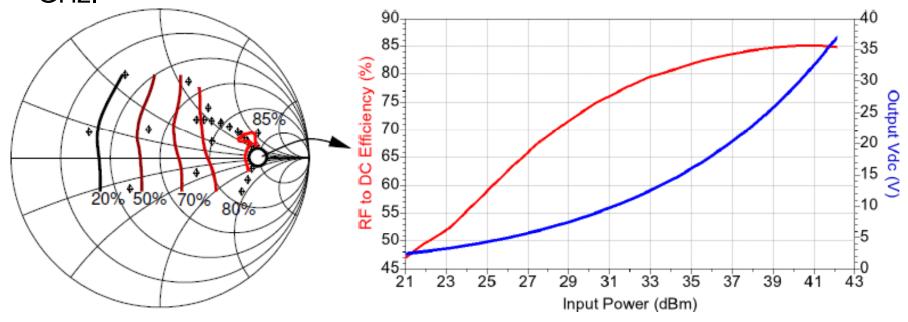

#### Simulated load pull

Simulated Class-F GaN transistor rectifier gate-port load-pull contours

- Optimal impedance for conversion efficiency at 2.14GHz shown

- Related to dynamic load-line with minimal enclosed area

- Close to the I-V characteristic at constant Vgs

Reveyrand, T., Ramos, Popovic, Z. "Time-reversal duality of high-efficiency RF power amplifiers," IET Electronics Letters, Dec.6 2012

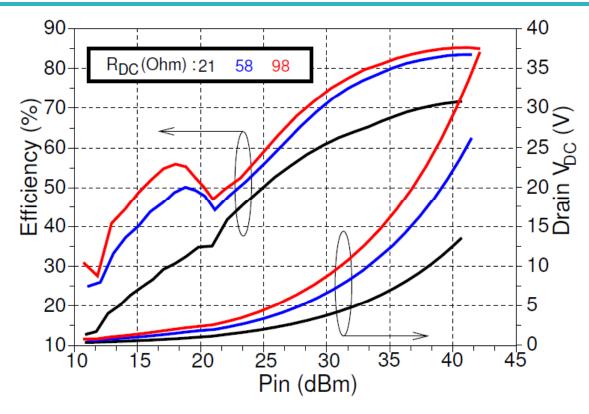

#### Rectifier efficiency

Rectifier performance measured at the coaxial reference planes at f=2.14 GHz.

RF load impedances used for measurements (black dots), where the contours correspond to max efficiency for the complete power sweep applied to the RF drain port.  $V_{DC}$  and efficiency measured for  $R_{DC}$  =98 $\Omega$  and Zload = (229 + j0.9) $\Omega$ .

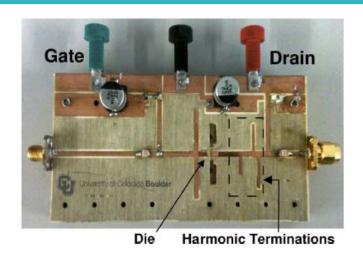

#### Measurements: Class F<sup>-1</sup>

Class-F-1 power amplifier based on TriQuint TGF2012 GaN 12-W die Pout=7W at f=2.14GHz PAE=84.6% at Vdd=31V with G=19dB (published)

Roberg, M., Hoversten, J., and Popovi´c, Z.: 'GaN HEMT PA with over 84% power added efficiency', Electronics Letters, 2010, 46, (23), pp. 1553-1554

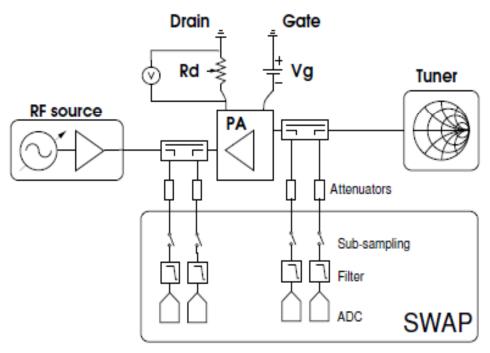

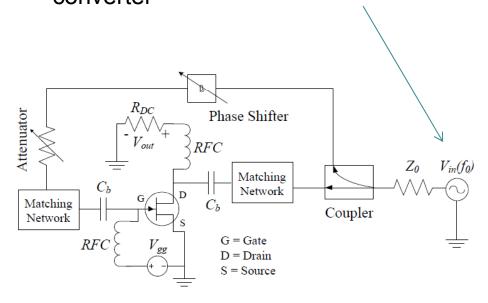

#### PA measured as rectifier

- An RF power sweep is performed at the input drain port for each RF impedance provided by the tuner at the gate port

- The output DC power delivered to the load RDC is calculated from the DC voltage as measured by a voltmeter

- Time-domain measurements

Rectifier load-pull measurement setup

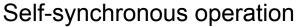

#### Measured time-domain waveforms

There is a gate signal with no gate input:

$$V_{gs} = -4.4 \text{ V}$$

$R_{dc} = 98.5 \Omega$

$Zg(f_0) = 230$

$+j0.1\Omega$

V2 and I2 are signals coupled to the gate matching network through Cgd.

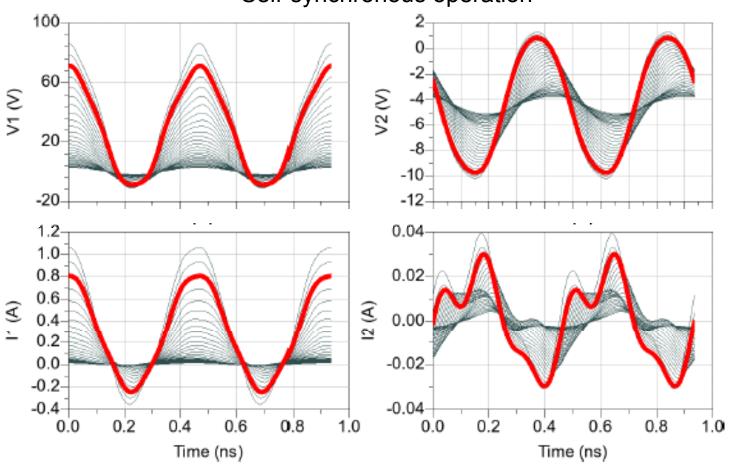

#### Measured efficiency and output voltage

- Efficiency greatly influenced by gate impedance

- $\eta_{max} = 85 \%$

- $P_{in}$  = 42 dBm

- $V_{dc} = 36 \text{ V}$

- Low gate impedance causes gate diode to conduct earlier

#### Rectifier conversion efficiency measurements

- Efficiency is greatly influenced by DC load

- High efficiency achieved at high input power and high output voltage

Vg= -4.4 V, Zg(f<sub>0</sub>)= 230+ j10 Ω

$$\eta_{max}$$

= 85 % with P<sub>in</sub> = 40 dBm and R<sub>dc</sub> = 98 Ω

Roberg, M., et al., "High-Efficiency Harmonically-Termindated Diode and Transistor Rectifier," Microwave Theory and Techniques, IEEE Transactions on , (Accepted)

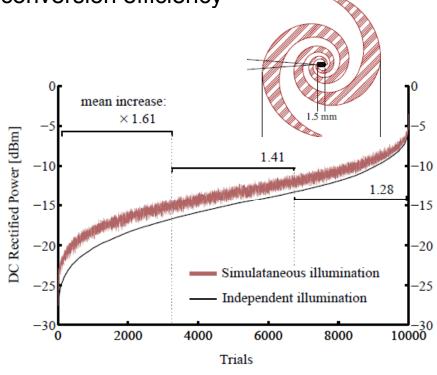

#### LF modulation of input RF for rectifiers

Modulate input frequency or PWM to control output DC voltage in DC-DC converter

"A UHF Class E2 DC/DC Converter using GaN HEMTs," R. Marante, N. Ruiz, L. Rizo, L. Cabria, J. A. García, IEEE T-MTT, Dec. 2012

Modulate input frequency (multi-tone excitation) in order to improve conversion efficiency

J.A Hagerty, F.B. Helmbrecht, W. McCalpin, R. Zane, Z. Popovic, "Recycling ambient microwave energy with broadband rectenna arrays," 2004.

#### **Conclusions**

- Low-frequency measurements for microwave circuits are not well established or understood

- Currently, very expensive microwave oscilloscopes, or specialized nonlinear network analyzers are the only option

- There is a need for time-domain measurements that can handle very different time scales

- Simultaneous low and high-frequency measurements allow for new circuit approaches and designs

- In this talk, we showed some challenges in envelope-frequency transistor and PA measurements for high efficiency transmitters and rectifier measurements for power applications

Thank you!