# Two-Stage GaN HEMT Amplifier With Gate–Source Voltage Shaping for Efficiency Versus Bandwidth Enhancements

Alaaeddine Ramadan, Tibault Reveyrand, Audrey Martin, Jean-Michel Nebus, Philippe Bouysse, Luc Lapierre, Jean-François Villemazet and Stéphane Forestier

Published in IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, Volume 59, No. 3, March 2011, pp. 699-706.

# doi:10.1109/TMTT.2010.2095033

© 2010 IEEE Personal use of this material is permitted. However, permission to reprint/republish or redistribute this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE.

# Two-Stage GaN HEMT Amplifier With Gate–Source Voltage Shaping for Efficiency Versus Bandwidth Enhancements

Alaaeddine Ramadan, Tibault Reveyrand, *Member, IEEE*, Audrey Martin, Jean-Michel Nebus, Philippe Bouysse, Luc Lapierre, Jean-François Villemazet, and Stéphane Forestier

*Abstract*—In this paper a two-stage 2-GHz GaN HEMT amplifier with 15-W output power, 28-dB power gain, and 70% power-added efficiency (PAE) is presented.

The power stage is designed to operate under class F conditions. The driver stage operates under class  $F^{-1}$  conditions and feeds the power stage with both fundamental and second harmonic components. The inter stage matching is designed to target a quasi-half sine voltage shape at the intrinsic gate port of the power stage. The goal is to reduce aperture angle of the power stage and get PAE improvements over a wide frequency bandwidth.

In addition to the amplifier design description, this paper reports original time-domain waveform measurements at internal nodes of the designed two-stage power amplifier using calibrated high-impedance probes and large signal network analyzer. Furthermore, waveform measurements recorded at different frequencies show that aperture angle remains reduced over large frequency bandwidth. In this study, a PAE greater than 60% is reached over 20% frequency bandwidth.

Index Terms—Aperture angle, classes F and  $F^{-1}$ , GaN power amplifier (PA), power-added efficiency (PAE), waveform measurements.

#### I. INTRODUCTION

**T** HE POWER amplifier (PA) remains a critical component in radio communication systems because it is an important energy consumer that impacts significantly the overall power consumption budget of a radio transmitter. Consequently, designing high-efficiency amplifiers is of prime importance to reduce power consumption, cooling requirements, and cost in RF transmit subsystem and to improve reliability aspects.

AlGaN/GaN HEMT technology has demonstrated a strong potential for high-efficiency high-power microwave amplification because of high electron mobility, high power density, and

A. Ramadan, T. Reveyrand, A. Martin, J.-M. Nebus, and P. Bouyssee are with the XLIM Laboratory, UMR 6172, University of Limoges, 87060 Limoges, France (e-mail: alaaeddine.ramadan@xlim.fr; tibault.reveyrand@xlim.fr; audrey.martin@xlim.fr; jean-michel.nebus@xlim.fr; philippe.bouysse@xlim.fr).

L. Lapierre is with the French Space Agency (CNES), Toulouse 31055, France (e-mail: Luc.Lapierre@cnes.fr).

J.-F. Villemazet and S. Forestier are with Thales Alenia Space, Toulouse 31100, France (e-mail: jean-francois.villemazet@thalesaleniaspace.com; stephane.forestier@thalesaleniaspace.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TMTT.2010.2095033

high breakdown voltage. High power-added efficiency (PAE) performances of microwave PAs are reached by implementing appropriate source and load matching conditions at harmonics. A lot of stuides have been carried out to investigate and demonstrate optimization strategies and procedures to enhance PAE performances of microwave PAs [1]–[16]. During the past years, many high-efficiency class F, class  $F^{-1}$ , class J, class E, and class D<sup>-1</sup> GaN amplifiers have been reported [17]–[19]. Highefficiency performances and limitations of microwave PAs can be appreciated by observing the shape of voltage and current waveforms at transistor ports. Minimized overlapping between drain-current and drain-source voltage indicates a minimized dissipated power. Recently we have reported in [20] and [21] an experimental study and calibrated time-domain waveform measurements concerning PAE enhancement conditions of GaN HEMTs with active second harmonic injection at the gate port.

Following these studies, in this paper we present a two-stage GaN HEMT PA design. The driver stage provides appropriate second harmonic injection to the input of the power stage. An appropriate inter stage matching network has been designed to get a quasi-half-sine-wave gate–source voltage at the input of the power stage. In addition to the design of the PA, the main focus of this paper is to examine the aspect of enhanced PAE performances when the frequency is shifted away from the center frequency. This aspect concerning PAE versus bandwidth is not so frequently reported to authors' knowledge. Furthermore, an original point of the paper stands in accurate gate–source voltage waveform measurements at internal nodes of the amplifier at different operating frequencies to highlight appropriate operating conditions favorable to maintain very good PAE performances over a wide bandwidth.

This paper is organized as follows. In Section II, the principle used in this work to improve the PAE of a class F power transistor driven by a half-sine gate–source voltage is recapitulated and illustrated with simulation results. In Section III, the proposed two-stage PA design is presented and discussed. In Section IV, measurement results are given to validate the design methodology. A particular emphasis is laid on time-domain measurements at internal nodes of the PA using calibrated highimpedance probes and a large signal network analyzer (LSNA). Measurements of the gate–source voltage of the power stage are performed at different operating frequencies and are compared to the measurements of the gate–source voltage waveform of a single-stage class F amplifier having a conventional quarter-wavelength line topology at the gate port used either

Manuscript received October 05, 2010; revised October 11, 2010; accepted October 30, 2010. Date of publication December 17, 2010; date of current version March 16, 2011. This work was supported by the French Space Agency and by Thales Alenia Space.

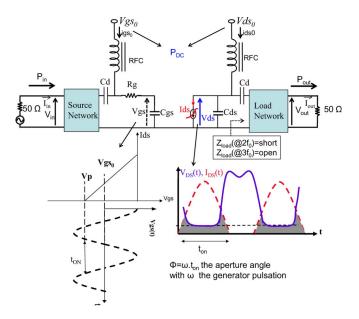

Fig. 1. Microwave class-F amplification principle and intrinsic waveforms.

for biasing the gate and having a short-circuit termination at the second harmonic.

# II. PAE IMPROVEMENT OF CLASS F GAN PA WITH A HALF-SINE-SHAPE GATE-SOURCE VOLTAGE

At microwave frequencies, high-efficiency PAs are tuned at the first three harmonics. For class F operation, the intrinsic drain–source voltage of transistors approximates a square wave and the intrinsic drain–current approximates a half sine wave, as illustrated in Fig. 1.

The gate–source bias voltage  $Vgs_0$  is close to or a little above the pinch-off voltage  $V_P$ . The RF gate–source voltage is a sine wave and load impedances at second and third harmonics are, respectively, close to a short and an open. Voltage and current waveform overlapping illustrated by the gray area in Fig. 1 must be reduced as much as possible to maximize efficiency.

A technique to improve PAE performances is to drive the gate of the transistor with a quasi-half-sine-wave voltage. To achieve such a gate–source voltage shaping, second harmonic (H2) injection is needed at the gate port. When applied to a class F amplifier, this technique lowers the turn on time  $(t_{on})$  of the drain–source current without affecting the square wave drain–source voltage, as reported in [20]. As a consequence, drain voltage and current overlapping is reduced and PAE performances are improved.

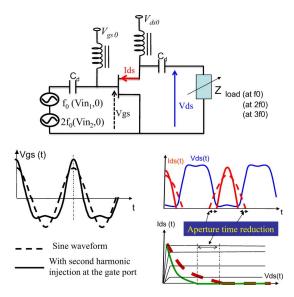

A nonlinear model of a 15-W die GaN HEMT from Cree, Durham, NC, has been extracted and harmonic-balance simulations have been performed using ADS software, as illustrated in Fig. 2. Time-domain waveforms plotted in dot lines are obtained when a sine-wave gate–source voltage Vgs(t) is applied (generator at  $2f_0$  is turned off). Time-domain waveforms plotted in solid lines are obtained when a quasi-half-sine-wave gate–source voltage is applied (both generators at  $f_0$  and  $2f_0$  are turned on). The ratio between the second harmonic and fundamental harmonic components is tuned to approximately 1/7. The

Fig. 2. Simulation methodology with second harmonic (H2) injection at gate port.

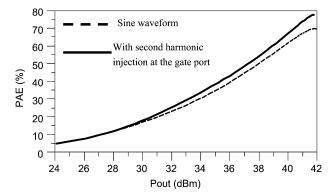

Fig. 3. Simulated PAE versus output power without (dotted line) and with (solid line) gate–source voltage shaping.

phase shift between fundamental and second harmonic components is close to  $0^{\circ}$ .

The aperture time reduction of the drain–source current and the corresponding dynamic load line modification obtained with half sine gate–source voltage shaping and observable in Fig. 2 illustrates the decrease of the overlap between drain–current and drain–source voltage.

Fig. 3 shows simulated PAE of the class F amplifier versus output power with and without gate–source voltage shaping. PAE enhancement of seven points is expected at high power.

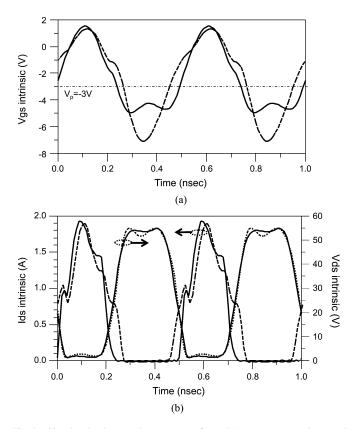

Time-domain voltage and current waveforms, as well as load lines recorded at 41.8-dBm output power are plotted in Figs. 4 and 5. A significant decrease of the turn on time  $(t_{on})$  of the drain–current can be clearly observed when a half-sine gate–source voltage waveform is applied.

A driver needed for an appropriate gate–source voltage shaping of power transistor is described in Section III.

## III. TWO-STAGE PA DESIGN

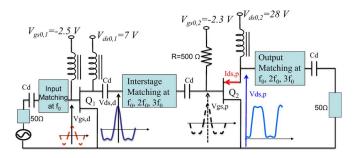

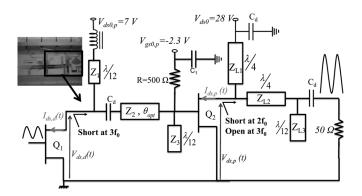

The proposed two-stage amplifier topology is illustrated in Fig. 6. The same HEMT GaN die (CGH60015D from Cree) is used for the driver stage (transistor  $Q_1$ ) and for the power stage

Fig. 4. Simulated voltage and current waveforms [(a) gate–source voltage and (b) drain–current and voltage]: sine shape gate–source voltage (dotted line), half sine shape gate–source voltage (solid line).

Fig. 5. Simulated load line without (dotted line) and with (solid line) second harmonic injection at the gate port.

(transistor  $Q_2$ ).  $Q_1$  is biased at  $V_{\rm gs0} = -2.5$  V and at a low drain voltage ( $V_{\rm ds0} = 7$  V) so that it does not affect the overall amplifier efficiency.  $Q_2$  is biased at  $V_{\rm gs0} = -2.3$  V and  $V_{\rm ds0} = 28$  V.

Load impedance of Q1 is high impedance at the second harmonic and low impedance (close to a short) at the third harmonic. Transistor Q1 used as a driver stage operates under class F-1 conditions. It produces an output half-sine drain voltage that feeds directly the gate port of the power stage.

Transistor Q2 operates under class F conditions with a proper half-sine shape gate-source voltage to enhance PAE, as explained in Section II. Load impedance of Q2 is low impedance

Fig. 6. Two-stage PA principle.

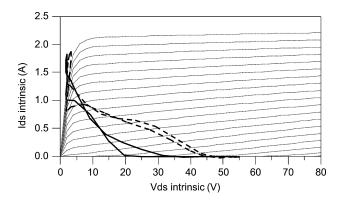

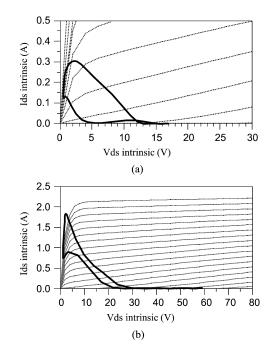

Fig. 7. Simulated intrinsic load line of: (a) Q1 and (b) Q2.

(close to a short) at the second harmonic and high impedance (close to an open) at the third harmonic. Simulated intrinsic dynamic load lines of transistor Q1 and Q2 operating at high level are shown in Fig. 7.

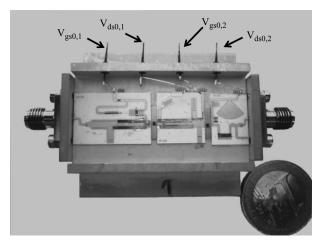

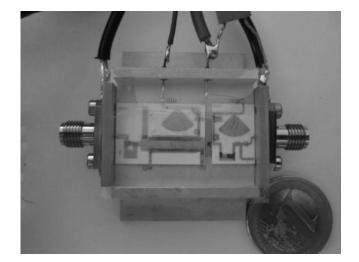

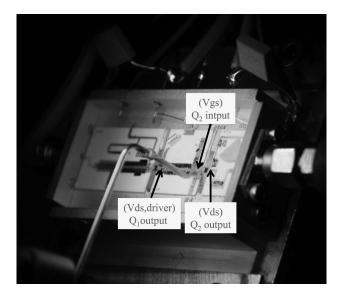

A photograph of the built amplifier is shown in Fig. 8.

Fig. 9 shows the design topology of the inter-stage matching network. The impedance at the third harmonic is shorted by an open stub  $(\lambda/12)$  connected close to the drain port of  $Q_1$ .  $Z_1$ ,  $Z_2$ ,  $Z_3$ , and the electrical length  $\vartheta_{opt}$  are optimized to reach a half-sine waveform at the input of the power stage, and the best load impedance of the driver stage at the fundamental and second harmonic.

The output matching circuit is synthesized to achieve impedance transformation from a 50- $\Omega$  load to the suitable optimum impedance at the fundamental, while the second harmonic is terminated into a short by the quarter-wavelength connected close to drain port of power stage. The third harmonic is terminated into an open.

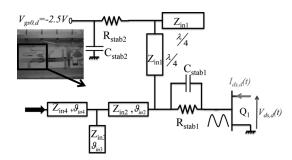

RC networks  $(R_{\text{stab1}}, C_{\text{stab1}}, R_{\text{stab2}}, C_{\text{stab2}})$ , shown in Fig. 10, have been added at the input of the driver stage to ensure stability.

Fig. 8. Photograph of the two-stage amplifier.

Fig. 9. Inter-stage and output stage design concept.

Fig. 10. Input matching network of the driver stage.

# IV. MEASUREMENT RESULTS

First, conventional input/output power measurements of the built amplifier have been performed. Second, a more in-depth characterization step has been achieved that consists of voltage waveform measurements at internal nodes of the two-stage circuit using an LSNA and high-impedance probes. To demonstrate PAE enhancement provided by our proposed technique, over an enlarged bandwidth, waveform measurements are compared to those measured on a single-stage class F PA. The reference single-stage class F PA shown in Fig. 11 is similar to the power stage of the two-stage PA previously described. The only difference lies in the quarter-wavelength line used either for biasing the gate and having at the input a short-circuit termination at second harmonic.

Fig. 11. Photograph of the input/output harmonics-tuned class F PA.

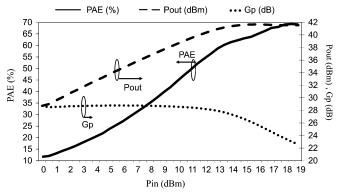

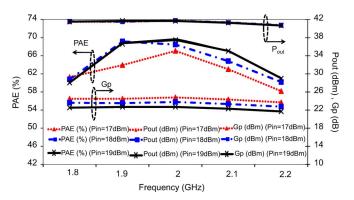

Fig. 12. Measured two-stage amplifier performances versus input power at 2 GHz.

Fig. 13. Measured two-stage amplifier performances versus frequency at 2-, 3-, and 4-dB gain compression.

## A. Power Measurements

Output power (Pout), PAE, and power gain (Gp) of the two-stage PA measured at 2-GHz center frequency and plotted versus input power (Pin) are given in Fig. 12. 28-dB power gain, 41.6-dBm output power, and 70% PAE are obtained. In Fig. 13, output power, PAE, and power gain are plotted versus frequency at 2-, 3-, and 4-dB gain compressions. The PA exhibits a PAE higher than 60% over a 400-MHz bandwidth.

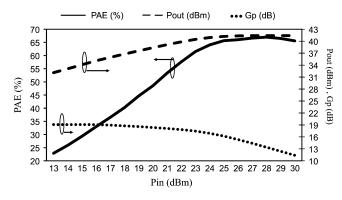

PAE, power gain, and output power of the single-stage PA recorded at 2 GHz are shown in Fig. 14. 66% PAE, 18-dB power

Fig. 14. Measured single-stage class F amplifier performances versus input available power at 2 GHz.

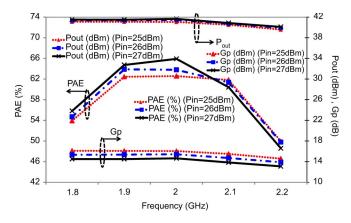

Fig. 15. Measured single-stage class F amplifier performances versus frequency at 2-, 3-, and 4-dB gain compression.

Fig. 16. PAE performances of the two PAs versus frequency at different output power levels.

gain, and 41.6-dBm output power are reached. The same output power as the one provided by the two-stage design is obtained and the PAE is four points lower.

This little difference in terms of PAE can be attributed to little difference in terms of gain compression.

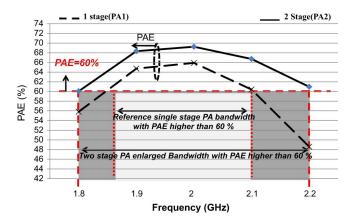

In Fig. 15, output power, PAE, and power gain of single-stage PA are plotted versus frequency at 2-, 3-, and 4-dB gain compressions. It can be observed that the single-stage PA exhibits a PAE higher than 60% on limited bandwidth of 200 MHz.

An interesting aspect, which is the main focus of this paper, can be observed in Fig. 16 where PAE performances of the two

Fig. 17. Built-in amplifier with high impedance probe.

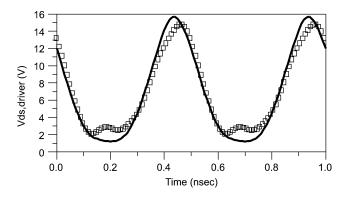

Fig. 18. Drain voltage of the driver stage. Measurement (square), simulation (solid line).

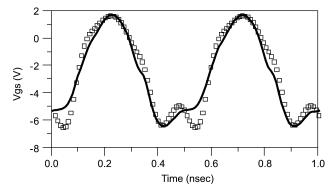

Fig. 19. Gate-source voltage of the power stage. Measurement (square), simulation (solid line).

PAs are plotted versus frequency at about 4-dB gain compression.

The use of a driver stage does not impact the overall PAE of the two-stage PA. It can be observed that the active gate–source voltage-shaping technique reported here offers significant improvement of PAE versus frequency. The frequency bandwidth corresponding to a PAE higher than 60% is augmented by a factor of 2. Time-domain waveforms measured at internal nodes of the PAs are given in the following (Section IV-B).

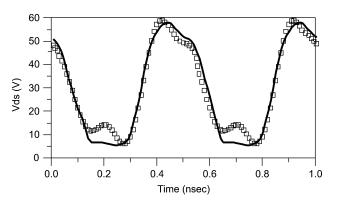

Fig. 20. Drain-source voltage of the power stage. Measurement (square), simulation (solid line).

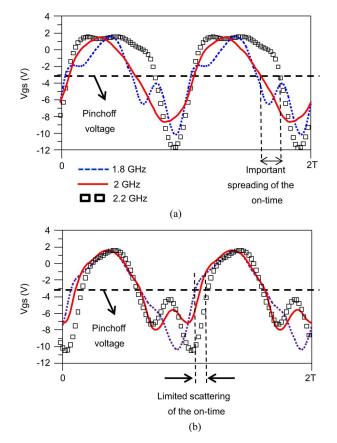

Fig. 21. Gate voltage waveforms measurements (normalize to 2T) at different frequencies (1.8–2.2 GHz). (a) Single-stage amplifier PA1. (b) Power stage of the two-stage PA PA2.

#### B. Time-Domain Waveform Measurements

Time-domain waveform measurements have been performed by using high-impedance probes (Fine Pitch Microprobes FPM  $20 \times$  from Cascade Microtech, Beaverton, OR), and an LSNA. Measurement principle and calibration procedure have been already reported in [22]. A photograph of the built-in amplifier and high-impedance probe used for RF voltage measurements is shown in Fig. 17.

1) Waveform Measurements at Center Frequency: Measured drain voltage waveform of the driver stage  $Q_1$  recorded at 41.5-dBm output power and 2-GHz center frequency is plotted in Fig. 18. Such measurements validate the inverse class F operation mode of the driver stage.

Measured gate voltage waveform of the power stage  $Q_2$  recorded at 41.5-dBm output power and 2-GHz center frequency is plotted in Fig. 19. Measurements are in good agreement with simulation results and demonstrate the good gate waveform shaping provided by the proposed inter-stage matching circuit.

Measured drain voltage waveform of the power stage  $Q_2$  recorded at 41.5-dBm output power and 2-GHz center frequency is plotted in Fig. 20. Such measurements validate the class F operation mode of the power stage.

2) Gate–Source Waveform Measurements at Different Frequencies: Gate–source voltage waveforms of the power stage recorded at different frequencies are plotted in Fig. 21. In order to observe the variation of the aperture angle, such voltage waveforms are normalized to two time periods (2T).

Fig. 21(a) corresponds to gate–source voltage waveforms of single-stage PA. Fig. 21(b) corresponds to gate–source voltage waveforms of the power stage of the two-stage PA.

It is shown that good PAE performances versus frequency (previously observable in Fig. 16) are attributed to the fact that there is a limited scattering of the on-time when the operating frequency changes in the case of the two-stage PA reported here compared to the case of the single-stage PA.

### V. CONCLUSION

This paper has presented a two-stage high-efficiency GaN PA. The driver stage operates at saturated level under inverse class F conditions with a low drain bias voltage. The power stage operates under class F conditions and high drain voltage. Such an amplifier addresses constant envelope signal amplification.

The most important aspect reported in this paper concerns the gate–source voltage-shaping technique applied to a class F power stage. An appropriate inter-stage matching circuit has been design to feed the power stage input with a half-sine voltage waveform.

This waveform shaping has been validated by time-domain measurements. Furthermore, it has been demonstrated that this technique enables an enlarged frequency bandwidth at high PAE. In the present case, PAE performances are better than 60% over a 400-MHz bandwidth.

#### ACKNOWLEDGMENT

The authors wish to acknowledge D. Geffroy, H. Yahi, and C. Baulon, all engineers with Thales Alenia Space, Toulouse, France, for their helpful assistance with fabricating and testing the PAs.

This work was performed in the context of a doctoral thesis with the Department of Nonlinear Microwave Circuit and System, XLIM Laboratory, Limoges University, Limoges, France.

#### REFERENCES

- P. Colantonio, F. Giannini, and E. Limiti, *High Efficiency RF and Microwave Solid State Power Amplifiers*. New York: Wiley, 2009.

- [2] A. Grebennikov and N. O. Sokal, Switch Mode RF Power Amplifiers. Oxford, U.K.: Newnes, 2007.

- [3] S. C. Crips, Advanced Techniques in RF Power Amplifier Design. Boston, MA: Artech House, 2002.

- [4] F. H. Raab, "Class E, class C, and class F power amplifiers based upon a finite number of harmonics," *IEEE Trans. Microw. Theory Tech.*, vol. 49, no. 8, pp. 1462–1468, Aug. 2001.

- [5] P. Colantonio, F. Giannini, G. Leuzzi, and E. Limiti, "Multiharmonic manipulation for highly efficient microwave power amplifiers," *Int. J. RF Microw. Comput.-Aided Eng.*, vol. 11, pp. 366–384, Nov. 2001.

- [6] P. Colantonio, F. Giannini, E. Limiti, and V. Teppati, "An approach to harmonic load- and source-pull measurements for high-efficiency PA design," *IEEE Trans. Microw. Theory Tech.*, vol. 52, no. 1, pp. 191–198, Jan. 2004.

- [7] P. Colantonio, F. Giannini, G. Leuzzi, and E. Limiti, "High efficiency low-voltage power amplifier design by second-harmonic manipulation," *Int. J. RF Microw Comput-Aided Eng*, vol. 10, pp. 19–32, 2000.

- [8] M. Akkul, M. Roberts, V. Walker, and W. Bosch, "High efficiency power amplifier input/output circuit topologies for base station and WLAN applications," in *IEEE MTT-S Int. Microw. Symp. Dig.*, 2004, pp. 843–846.

- [9] J. Staudinger, "Multiharmonic load termination effects on GaAs power amplifiers," *Microw. J.*, pp. 60–77, Apr. 1996.

- [10] Y. Y. Woo, Y. Yang, and B. Kim, "Analysis and experiments for highefficiency class-F and inverse class-F power amplifiers," *IEEE Trans. Microw. Theory Tech.*, vol. 54, no. 5, pp. 1969–1974, May 2006.

- [11] S. Mazumder, A. Azizi, and F. Gardiol, "Improvement of class-C transistor power amplifier by second-harmonic tuning," *IEEE Trans. Microw. Theory Tech.*, vol. MTT-27, no. 5, pp. 430–433, May 1979.

- [12] P. White, "Effect of input harmonic terminations on high efficiency class B and class F operation of PHEMT devices," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 7–12, 1998, vol. 3, pp. 1611–1614.

- [13] B. Ingruber, W. Pritzl, D. Smely, M. Wachutka, and G. Magerl, "Harmonic-controlled amplifier," *IEEE Trans. Microw. Theory Tech.*, vol. 46, no. 6, pp. 857–863, Jun. 1998.

- [14] S. Gao, P. Butterworth, S. Ooi, and A. Sambell, "High-efficiency power amplifier design including input harmonic termination," *IEEE Microw. Wireless Compon. Lett.*, vol. 16, no. 2, pp. 81–83, Feb. 2006.

- [15] M. Maeda, H. Masato, H. Takehara, M. Nakamura, S. Morimoto, H. Fujimoto, Y. Ota, and O. Ishikawa, "Source second-harmonic control for high efficiency power amplifiers," *IEEE Trans. Microw. Theory Tech.*, vol. 43, no. 12, pp. 2952–2957, Dec. 1995.

- [16] F. Blache, "A novel computerised multiharmonic active load-pull system for the optimization of high efficiency operating classes in power transistors," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Orlando, FL, Jun. 1995, pp. 1037–1040.

- [17] D. Schmelzeral, "A GaN HEMT class F amplifier at 2 GHz with >80% PAE," *IEEE J. Solid-State Circuits*, vol. 42, no. 10, pp. 2130–2136, Oct. 2007.

- [18] P. Wright, J. Lees, P. J. Tasker, J. Benedikt, and S. C. Cripps, "An efficient, linear, broadband class-J-mode PA realized using RF waveform engineering," in *IEEE MTT-S Int. Microw. Symp. Dig.*, 2009, pp. 653–656.

- [19] U. Gustavsson, T. Lejon, C. Fager, and H. Zirath, "Design of highly efficient, high output power, *L*-band class *D*<sup>-1</sup> RF power amplifiers using GaN MESFET devices," in *Proc. Eur. Microw. Assoc.*, 2007, pp. 1089–1092.

- [20] A. Ramadan, T. Reveyrand, A. Martin, J. M. Nebus, P. Bouysse, L. Lapierre, J. F. Villemazet, and S. Forestier, "Experimental study on effect of second-harmonic injection at input of classes F and F<sup>-1</sup> GaN power amplifiers," *Electron. Lett.*, vol. 46, no. 8, pp. 570–572, Apr. 2010.

- [21] A. Ramadan, T. Reveyrand, A. Martin, J. M. Nebus, P. Bouysse, L. Lapierre, J. F. Villemazet, and S. Forestier, "Efficiency enhancement of GaN power HEMTs by controlling gate-source voltage waveform shape," in *Eur. Microw. Conf.*, Rome, Italy, 2009, pp. 487–490.

- [22] T. Reveyrand, A. Mallet, J. M. Nebus, and V. M. Bossche, "Calibrated measurements of waveforms at internal nodes of MMICs with a LSNA and high impedance probes," in *62nd ARFTG Conf. Dig.*, Boulder, CO, Dec. 2003, pp. 71–76.

**Alaaeddine Ramadan** was born in Barja, Lebanon, on March 7, 1985. He received the Ph.D. degree in microwave communication engineering from the University of Limoges, Limoges, France, in 2010.

He is currently a Postdoctoral Fellow with the XLIM Laboratory, University of Limoges. His research interests include modeling of microwave transistors and optimization of microwave PAs.

components.

**Tibault Reveyrand** (M'07) was born in Paris, France, in 1974. He received the Ph.D. degree from Limoges University, Limoges, France, in 2002.

From 2002 to 2004, he was a Post-doctoral Scientist with the Centre National d'Etudes Spatiales (CNES) (French Space Agency). In 2005, he became a Contractual Engineer with the Centre National de la Recherche Scientifique (CNRS), XLIM Laboratory (formerly IRCOM), Limoges, France. His main research interests include the characterization and the modeling of RF and microwave nonlinear

Audrey Martin was born in Châteauroux, France, in 1980. She received the Ph.D. degree from Limoges University, Limoges, France, in 2007.

She is currently a Teacher and Researcher with the XLIM Laboratory, University of Limoges, Limoges, France. Her main research interests include active microwave and millimeter-wave circuit design, wideband PAs, and nonlinear modeling techniques.

Jean-Michel Nebus was born in Bourganeuf, France, in 1963. He received the Ph.D. degree in electronics from the University of Limoges, Limoges, France, in 1988.

He was a Project Engineer with Alcatel Space Industries, Toulouse, France. He is currently a Professor with the XLIM Laboratory, University of Limoges. His main research interest is nonlinear microwave device characterization and design.

**Philippe Bouysse** was born in Aurillac, France, on September 18, 1965. He received the Ph.D. degree in communication engineering from the University of Limoges, Limoges, France, in 1992.

Since 1992, he has been with the University of Limoges, Brive, France, as a Teacher and Researcher with the XLIM Laboratory. His main research interests are the modeling of microwave transistors and the design and optimization of microwave PAs.

Luc Lapierre was born in Clermont-Ferrand, France, in 1957. He received the Dipl-Ing degree from the Ecole Superieure d'Electricite (ESE), Paris, Gif sur Yvette, France, in 1980.

In December 1981, he joined the French National Space Centre (CNES), Toulouse, France, where he was involved in microwave research activities mainly oriented on solid-state components. He also provides technical support in the development of microwave equipments for satellite payloads. He has been the Head of the Microwave Department, CNES, and is

currently a Microwave Expert with the Microwave and Time Frequency Department, CNES.

**Jean-François Villemazet** received the Engineer degree in electronics and Ph.D. degree in electronics from the University of Limoges, Limoges, France, in 1989 and 1994, respectively.

In 1989, he joined the Thomson Company, where he studied mixer optimization. In 1994, he joined Alcatel Space Industries, where he designed numerous monolithic microwave integrated circuits (MMICs) and was involved with transistor nonlinear modeling. Since 1998, he has been studying the design of linearizers and PAs for satellite payloads. In 2003, he

was responsible for the MMIC design team of Thales Alenia Space, Toulouse, France. Since 2007, he has been responsible for a team dedicated to the advanced study of microwave equipments for satellite payloads. His research interests are nonlinear microwave circuit design and computer-aided design (CAD) methodologies.

**Stéphane Forestier** was born in Paris, France, on December 19,1975. He received the Electrical Engineering degree from the Ecole Polytechnique de l'Université de Nantes (EPUN), Nantes, France, in 2000, and the Ph.D. degree in microwave communication engineering from the University of Limoges, Limoges, France, in 2003.

In 2000, he joined IRCOM, where he was involved with high PA design methods and linearizer systems. In 2004, he joined Thales Alenia Space, Toulouse, France, where is currently an Advanced Study Engi-

neer involved in topics related to high-power applications such as characterization, modelization, simulation, and design.