# Session 3: Characterization and modeling

# Measurements for Optimization of Solid-State Power Amplifiers

### Jean-Pierre Teyssier, Tibault Reveyrand, Denis Barataud

XLIM C<sup>2</sup>S<sup>2</sup>, University of Limoges, 127 avenue Albert Thomas, 87000 Limoges, France

#### **Outline**

- Introduction

- Quick overview of classical measurement techniques for NL devices

- Memory effects characterization and modeling

- Waveform engineering based on measurements

- Envelope tracking dynamical biasing / pre-distortion

- High impedance probing

- Conclusion

# We all want more RF Power! High power measurements can be funny

### RF LDMOS - Bias Tee - Transmission line - Mismatched load

**Courtesy of Freescale**

© This is not exactly what we want, but there is a lot of RF power here!)

# Introduction: Transistor NL behavior with dynamical NL memory effects

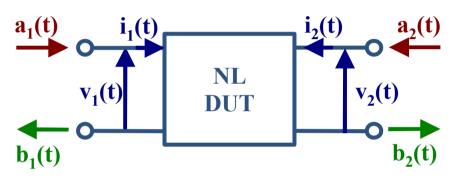

# Particular case of a nonlinear two-ports device with memory effects

4 instantaneous time-domain variables: I(V) or B(A)

$$\begin{cases} v_{i}(t) = \sqrt{Z_{0}} [a_{i}(t) + b_{i}(t)] \\ i_{i}(t) = \frac{[a_{i}(t) - b_{i}(t)]}{\sqrt{Z_{0}}} \end{cases} \quad i = (1, 2)$$

$\triangleright$  Device commands: incident waves  $a_1(t)$ ,  $a_2(t)$

**Instantaneous but recent history required**

**▶** Device response: reflected waves

$$\begin{cases} b_1(t) = \mathbf{f}_{NL} [a_1(t), a_2(t), \mathring{a}_1(t), \mathring{a}_2(t), \dots] \\ b_2(t) = \mathbf{g}_{NL} [a_1(t), a_2(t), \mathring{a}_1(t), \mathring{a}_2(t), \dots] \end{cases}$$

**Large number of terms for LF memory**

- **8** Signals with wideband modulations or large peak-to average are distorted

- **©** These distortions are deterministic, we can compute then (with great efforts!)

# Introduction: NonLinear Measurements Everywhere

# First-pass success of design / foundry process / tests of RF SSPAs

# NL Meas. for modeling:

- Transistor Model

- Physical phenomena models

- Memory effects

# NL Meas. for design:

- Wideband modulated signals

- Waveform engineering

- Envelope tracking data

- Pre-distortion data

# NL Meas. for verification/debug:

- Specifications

- Performances

- Reliability

- High Impedance probing

#### **Outline**

- Introduction

- Quick overview of classical measurement techniques for NL devices

- Memory effects characterization and modeling

- Waveform engineering based on measurements

- Envelope tracking dynamical biasing / pre-distortion

- High impedance probing

- Conclusion

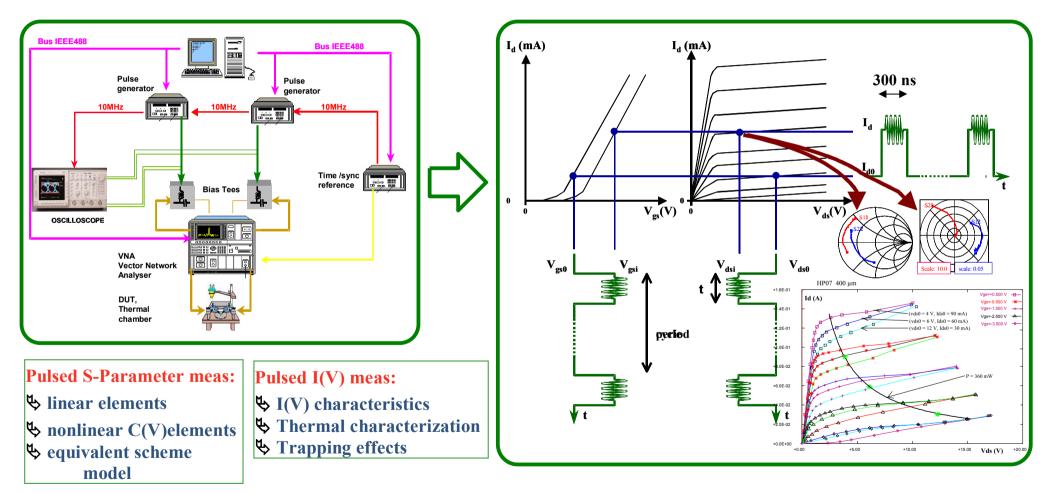

### Pulsed I(V) and Pulsed S-Parameters

### **Motivation for short pulses: Control of the device self-heating**

**⊗** Fast behavior of GaN devices (thermal, traps): ultra short pulses <50ns required

# Pulsed I(V) integrated systems available today

• Auriga/Diva AU4550

• Keithley 4200 SCS

• Agilent B1500A

Amcad IVCad-PIV

Focus Microwaves PIV

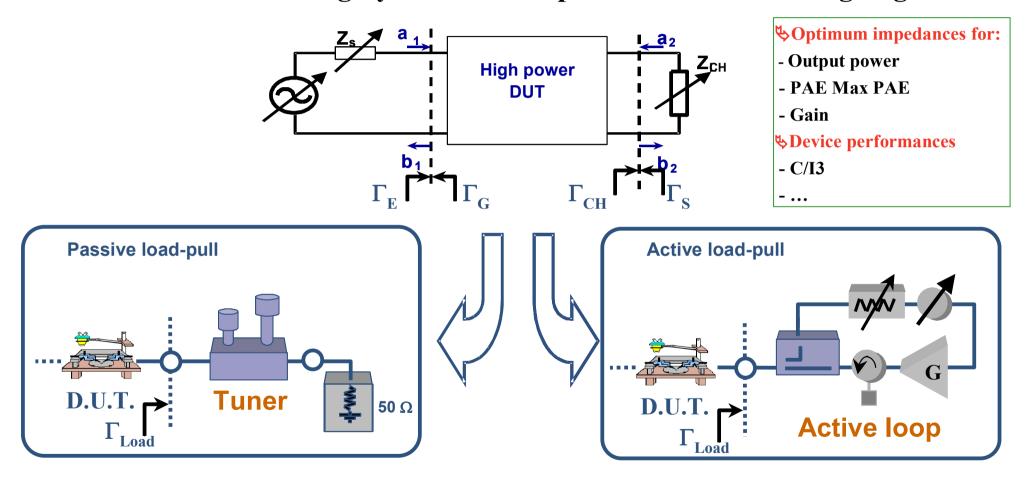

# Load-Pull and Source-Pull setups

# Measurement of highly mismatched power devices with large signals

© Possible improvements: pulsed or modulated signals, handling of harmonic frequencies

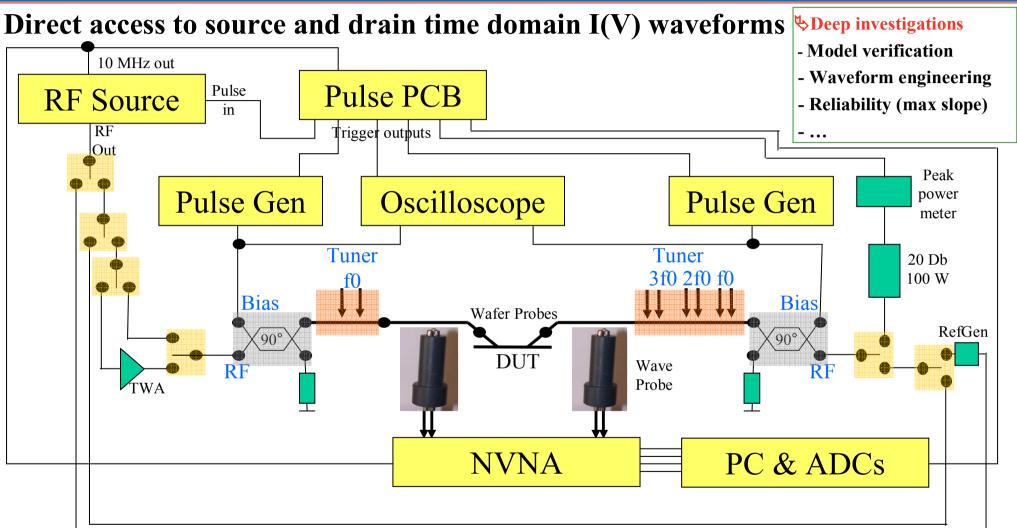

# Time domain Load-Pull Setup with NVNA receiver

© Special features: Wave probes, NVNA receiver, multi-harmonic tuning, hybrid bias tees

# NVNA (NonLinear Vector Network Analyzer) hardware available today

| RF heads   N | /lixer-based | Sampler-based |

|--------------|--------------|---------------|

|--------------|--------------|---------------|

Donwconversion

Frequency by frequency acquisition

(needs a phase reference

One-shot acquisition of all frequencies

(a sampler as phase reference)

Agilent NVNA

R&S ZVA+ NMDG

Anritsu VectorStar + HFE

VTD SWAP X402 (formerly the MTA, the LSNA)

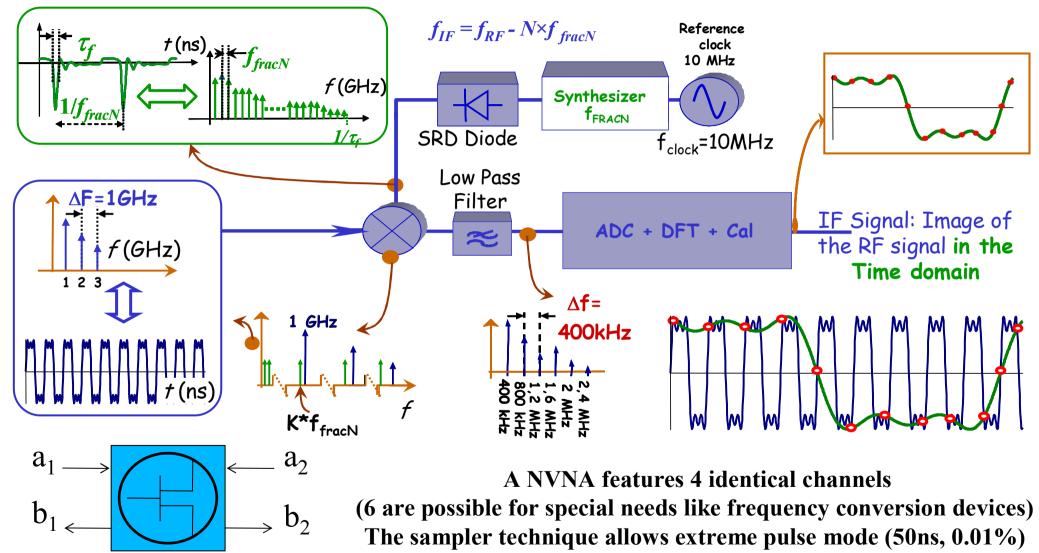

# Sampler-based NVNA wideband down-conversion principle

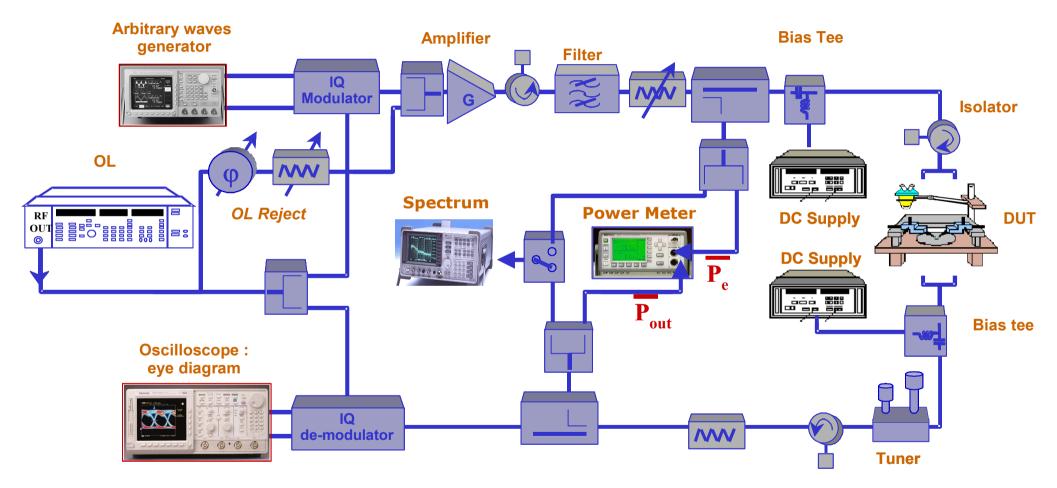

# Envelope measurement set-up

# NonLinear behavior of RF power amplifiers when a modulated signal is applied

**8** Needs a specific and complex calibration procedure

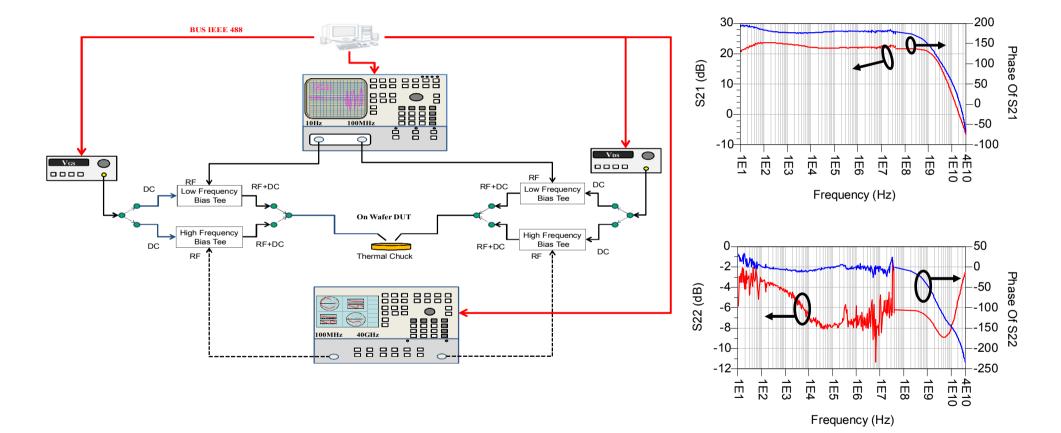

# Low-frequency small signal analysis

# Measurements from 10 Hz to 40 GHz

Special low frequency bias tees have been designed

# Quick overview of possible test signals

Vienna, April 18th-19th, 2011

# Simple RF test signals:

⇔ one-tone (CW):

S-parameters, AM/AM and AM/PM, constant envelope

Waveform distortion, compression

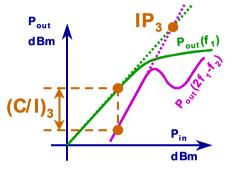

**♦** 2-tones, 3 tones :

$\Leftrightarrow$

Intermodulation C/I, IP, LF memory, variable envelope, peak to average

**Envelope distortion**

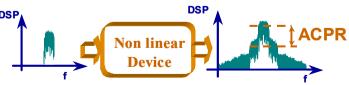

# Complex RF test signals:

> Multitone signals :

Noise Power

Ratio

Signal distortion

**♦** Modulated carrier :

Adjacent Channel Power Ratio

**Dynamical behavior of NonLinearities**

#### Tentative chart of RF measurement instruments

Complex of use Ease

Simple

Time domain

**Frequency** domain

**Power** detection

Scalar networks **Spectrum analyzers Powermeters**

**NVNA Sampling Scopes VSA**

Vector Network analyzers

New!

Fast **Arbitrary** Wave Generator

- **Absolute power**

- Harmonic distortion

- **ĕ** Image reject

- **Oscillator stability**

- **NPR/ACPR**

poor

- **Gain**

- **Linearity** [S] pulsed

- SWR **Compression ĕ** Impedance **ĕ** Group delay

- **Pulse profile Isolation**

- **Distortion**

- Time domain

- **Error** rate

- **Modulation**

- **Eye diagram**

**Information**

large

#### **Outline**

- Introduction

- Quick overview of classical measurement techniques for NL devices

- Memory effects characterization and modeling

- Waveform engineering based on measurements

- Envelope tracking dynamical biasing / pre-distortion

- High impedance probing

- Conclusion

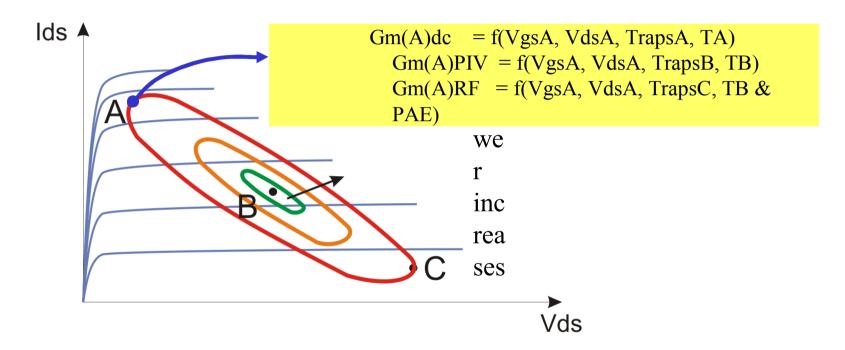

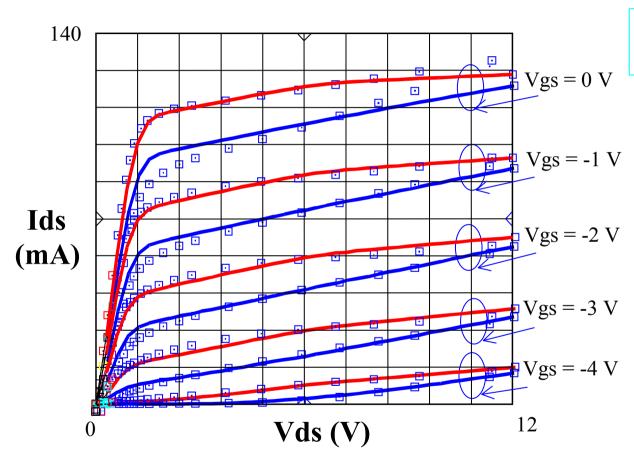

### Discrepancy between DC and RF behavior

# **Gm** at point A versus measurement conditions

We get 3 very different values of Gm. Y21  $\neq$  dID/dVDS Consequences of low frequency memory effects on drain current (thermal effect and trapping effects)

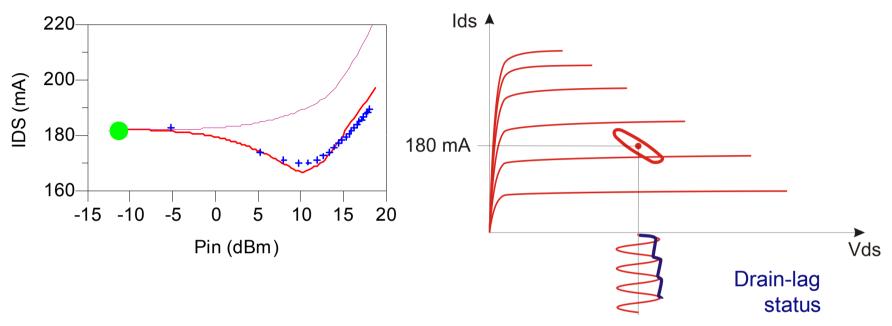

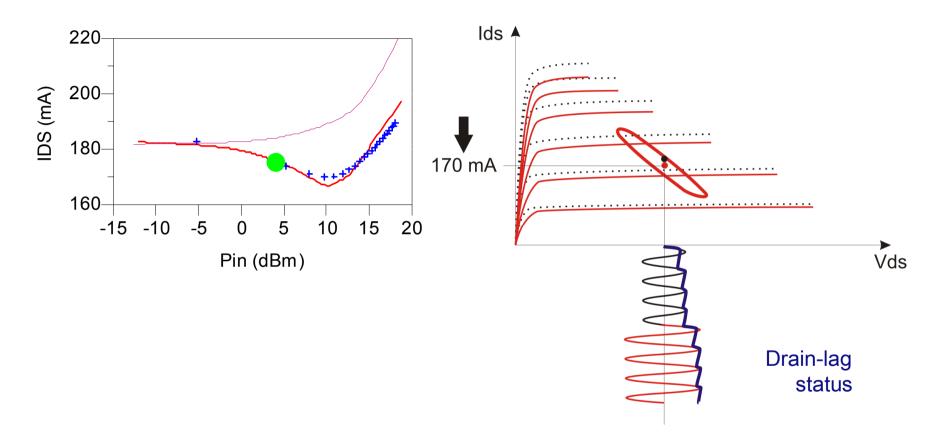

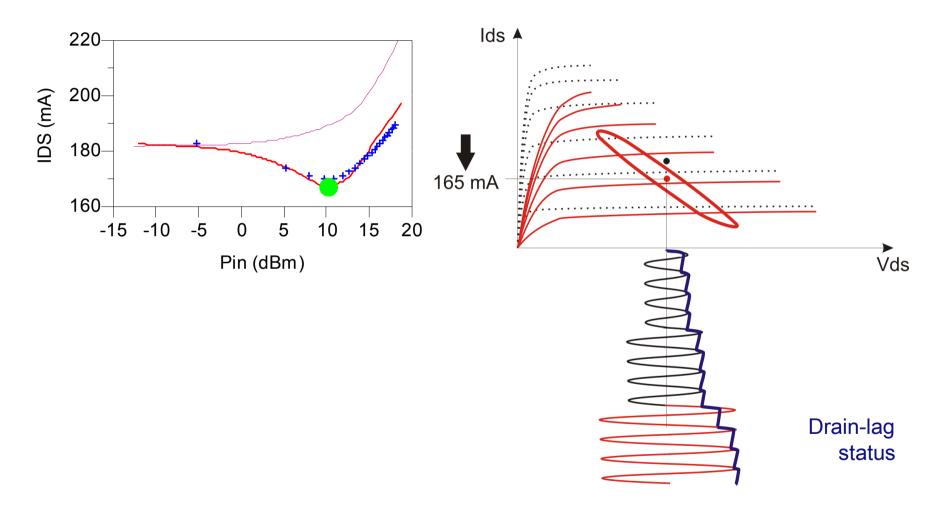

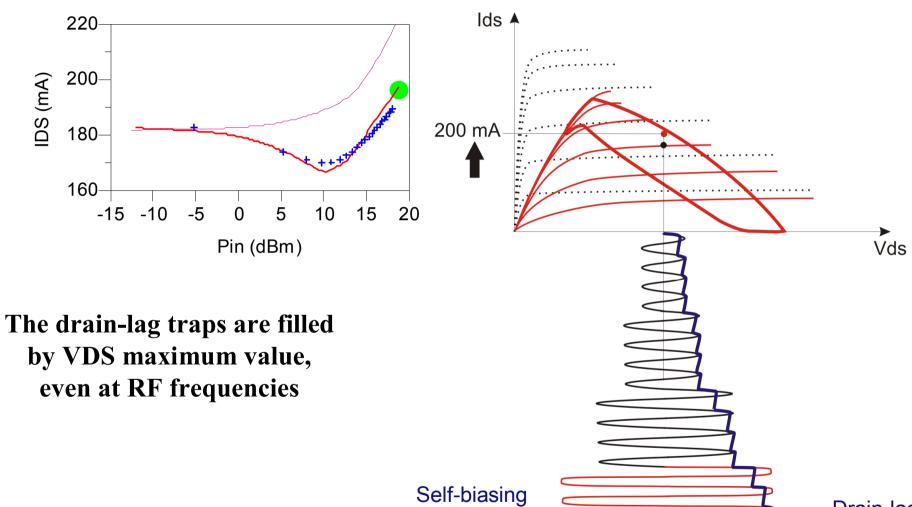

# Bias current versus input power (1/4)

# Bias current versus input power (2/4)

# Bias current versus input power (3/4)

# Bias current versus input power (4/4)

Drain-lag

status

# Effect of PIV DC point on I(V) characteristics

Vds0 = 12V Ids0 = 30 mA

Vds0 = 4VIds0 = 90 mA

The device temperature is identical, thus the discrepancy is due to drain lag effects

The PIV measurements put in evidence trapping memory effects

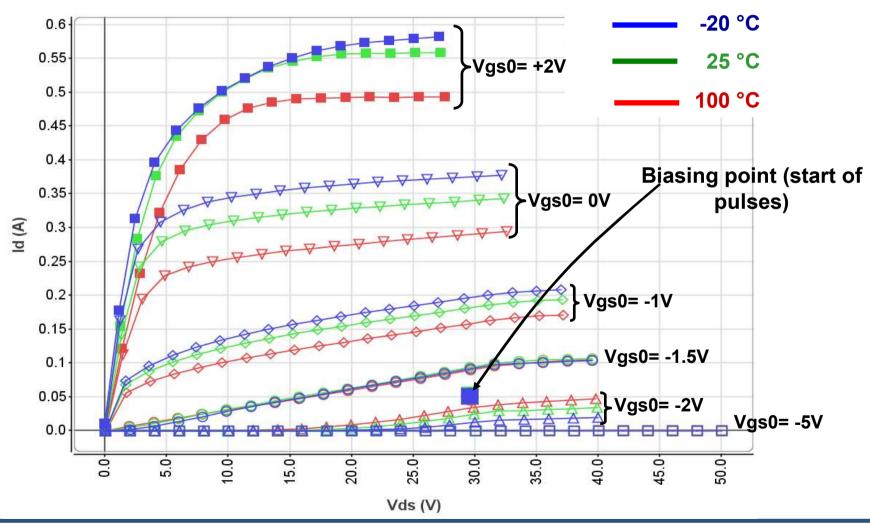

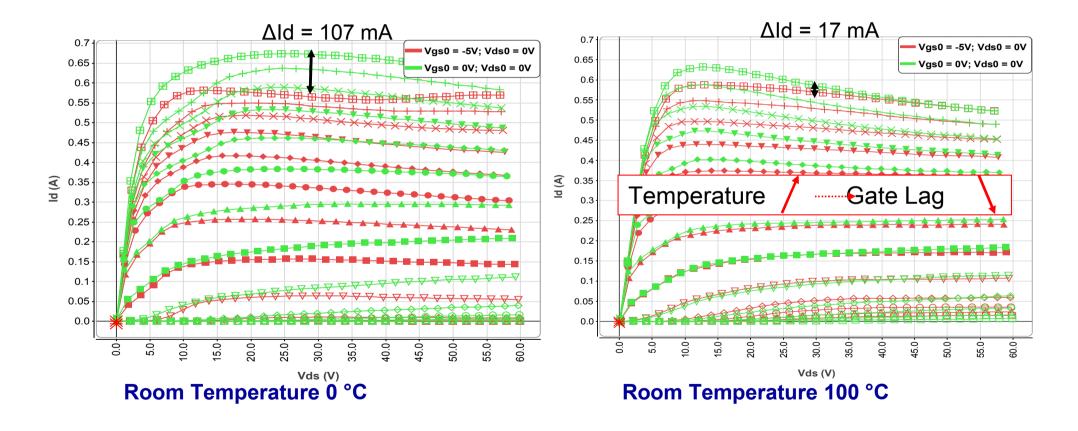

# PIV for different room temperatures

# GaN 8x75 μm, Pulses 700ns, Period 1ms, hot biasing point

### PIV for different room temperatures

# GaN 8x75 μm, Pulses 700ns, Period 10 μs, cold VDS0=0 biasing point

Trap capture and emission time constants are varying versus temperature: Arrhenius

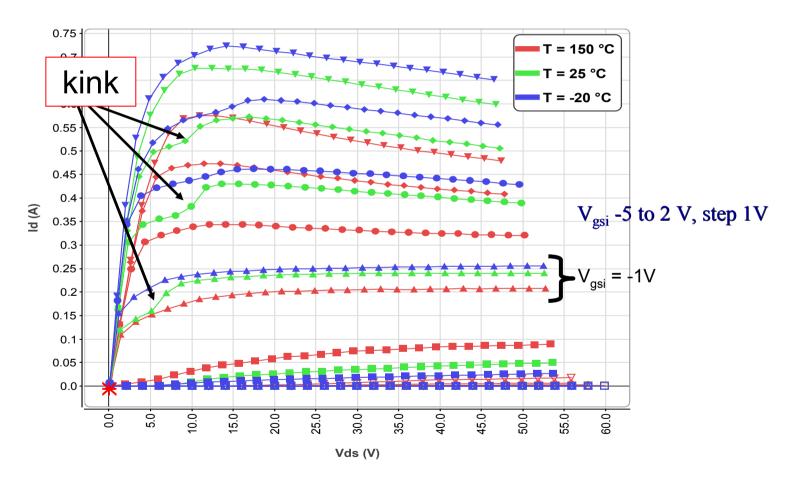

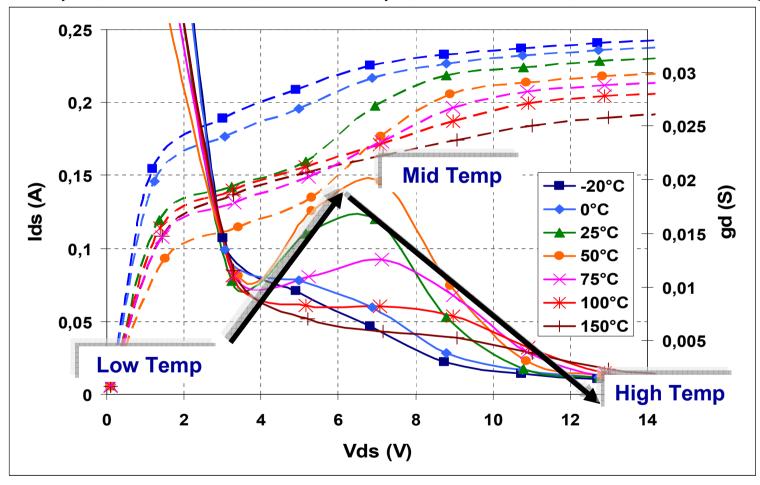

# Kink effect versus room temperatures 1/2

# GaN 8x75 μm, Pulses 700ns, Period 10 μs, cold VDS0=0, VGS0=0 biasing point

Kink effect only at intermediate temperatures

# Kink effect versus room temperatures 2/2

# GaN 8x75 μm, Pulses 700ns, Period 10 μs, cold VDS0=0, VGS0=0 biasing point

This effect is explained by the temperature dependance of trap emission time constant

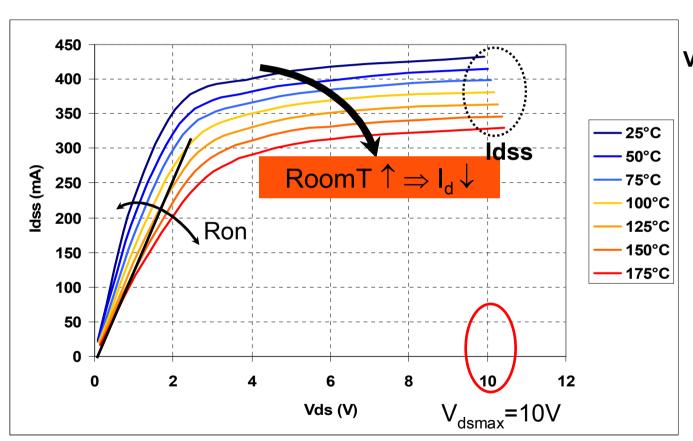

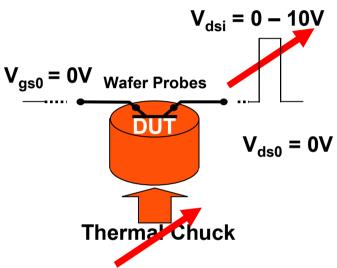

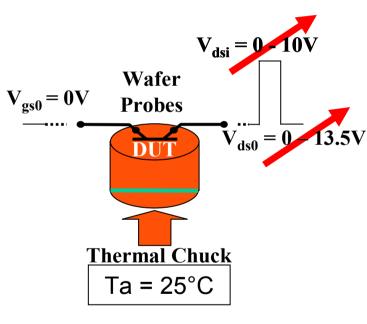

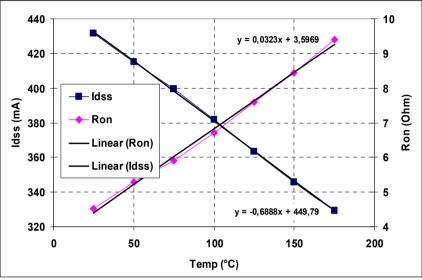

# Thermal resistance determination (1/3)

# Ron and Idss measurements at different base-plate temperatures

V<sub>gs0</sub>: gate bias point.

V<sub>ds0</sub>: drain bias point.

V<sub>dsi</sub>: drain pulsed point.

Pulsed I-V characteristics ( $V_{GS} = 0 \text{ V}$ ) from zero power bias point ( $V_{DS0} = V_{GS0} = 0 \text{ V}$ )

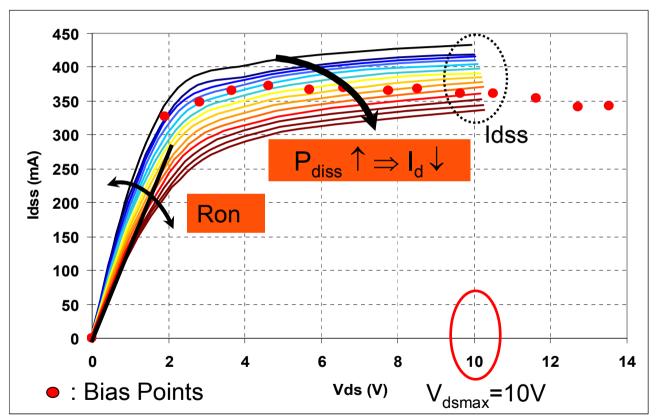

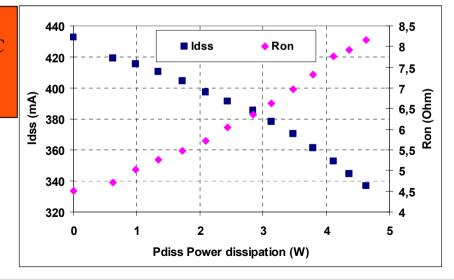

### Thermal resistance determination (2/3)

# Ron and Idss measurements for different dissipated power

Pulsed I(V) characteristics ( $V_{GSi} = 0 \text{ V}$ ) from various quiescent bias points (VGS0 = 0 V, VDS0 = 2-13.5 V) with fixed thermal chuck at 25 °C

# Thermal resistance determination (3/3)

Variable

Temp

Constant

Pdiss = 0W

Constant

Temp=25°C

Variable

Pdiss

# The Thermal Resistance is the ratio between the Ron slopes

$$R_{ON}(\Delta T) = R_{ON}(T_0) + \frac{dR_{ON}}{dT} \cdot \Delta T$$

$$R_{ON}(R_{ON}) = R_{ON}(R_{ON}) + \frac{dR_{ON}}{dR_{ON}} \cdot R_{ON}$$

$$R_{ON}(P_{diss}) = R_{ON}(0) + \frac{dR_{ON}}{dP_{diss}} \cdot P_{diss}$$

•

$$T_0=25$$

°C

•

$$\Delta T = T - T_0$$

$$R_{TH} = \frac{\Delta T}{\Delta P_{diss}} = \left(\frac{dR_{ON}}{dP_{diss}}\right) / \left(\frac{dR_{ON}}{dT}\right)$$

Self-heating during pulses is not an issue because we extract a slope

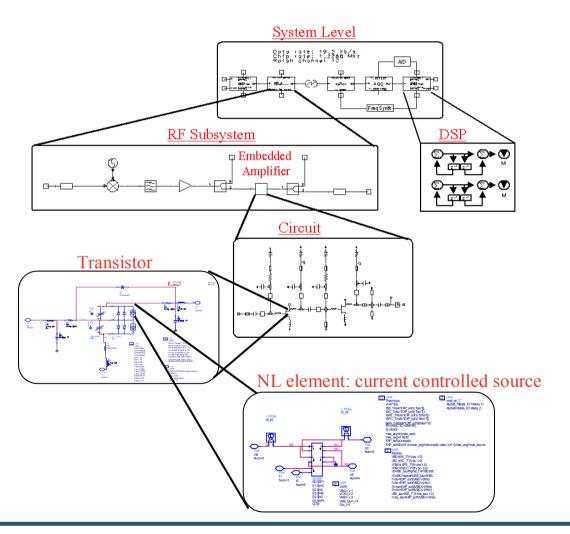

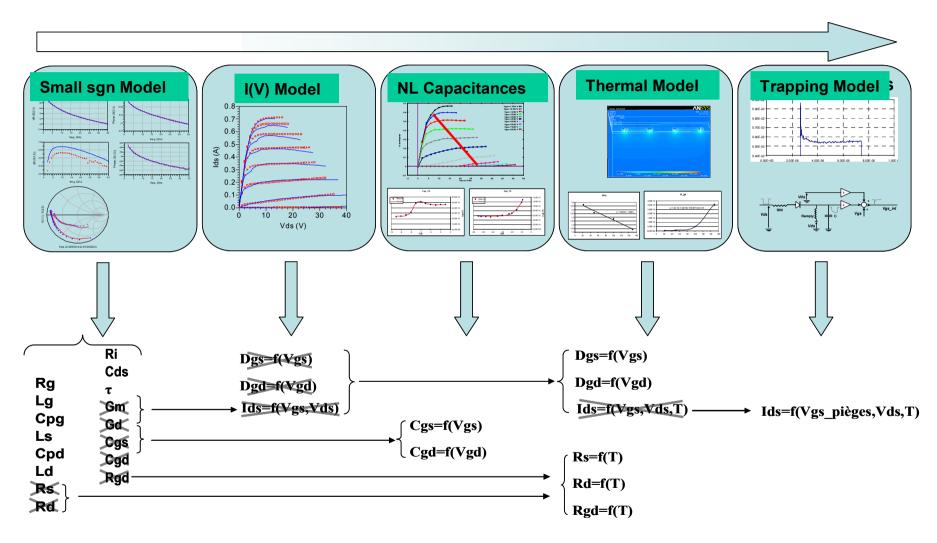

# Classic flow-chart of RF transistor NL modeling

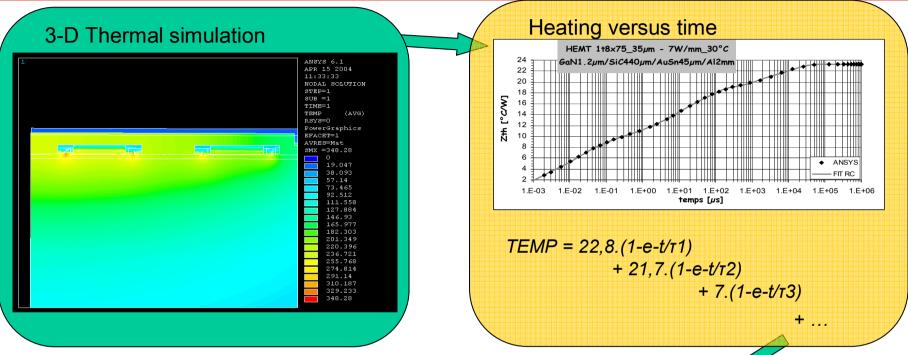

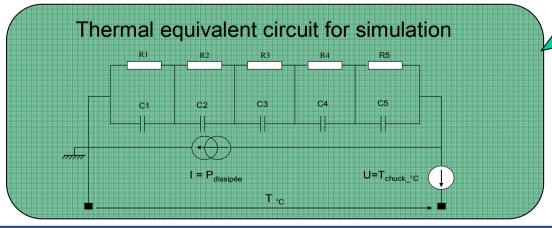

# Dynamical thermal behavior

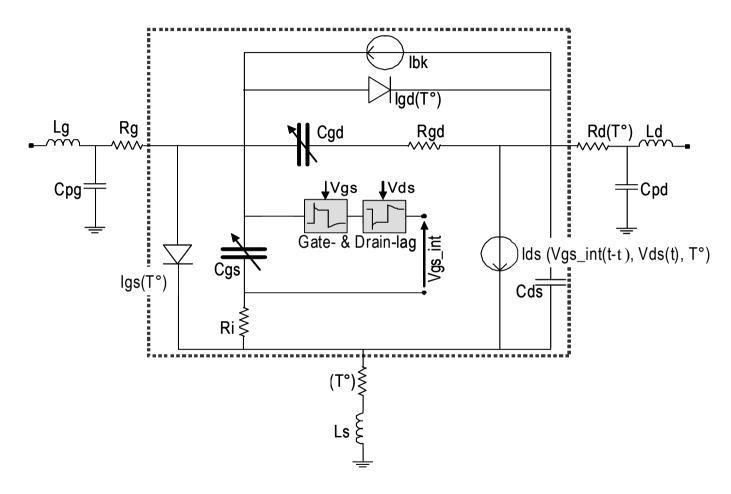

# NL FET model with trapping and thermal effects

This is a possible FET model amongst many "good agreement" or improved models!

Such a model cannot be perfect everywhere, the targeted application must be considered

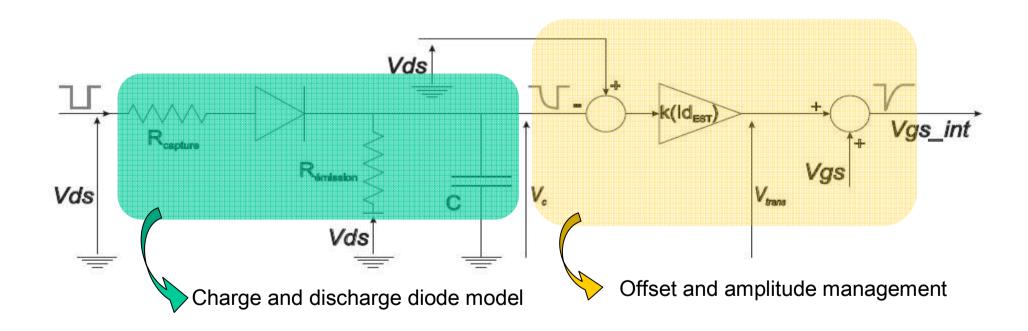

# Zoom into the trapping effect bloc (for one trap level)

The trap effects on drain current are taken into account by a modified VGS (Vgs\_int)

Note the unsymmetrical capture and emission effects modeled by the envelope detector

# Conclusions on LF memory effects

- We have shown some electrical effects of LF memory effects, there are many others:

- at circuit level when large peak to average are applied

- at system level (Bit Error Ratio)

- phase shifts are to be considered for RADAR applications...

- We have shown some techniques to characterize LF memory effects

- a lot of work is carried out in labs to find reliable techniques to separate trapping and thermal effects (same frequency range)

- fast pulses and very low frequency measurements are interesting ways

- We have shown some possible modeling approach based on equivalent circuit

- Many model topologies, equations and methods are available

- With improved Volterra models (like X-Parameters), long-term memory effects can now be taken into account with models driven by meas. data

#### **Outline**

- Introduction

- Quick overview of classical measurement techniques for NL devices

- Memory effects characterization and modeling

- Waveform engineering based on measurements

- Envelope tracking dynamical biasing / pre-distortion

- High impedance probing

- Conclusion

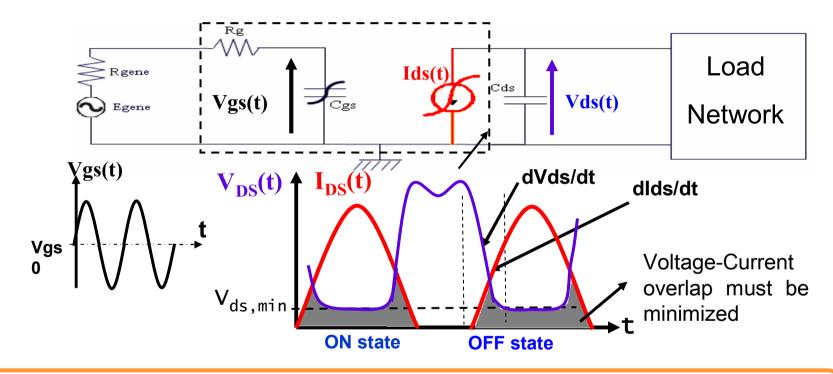

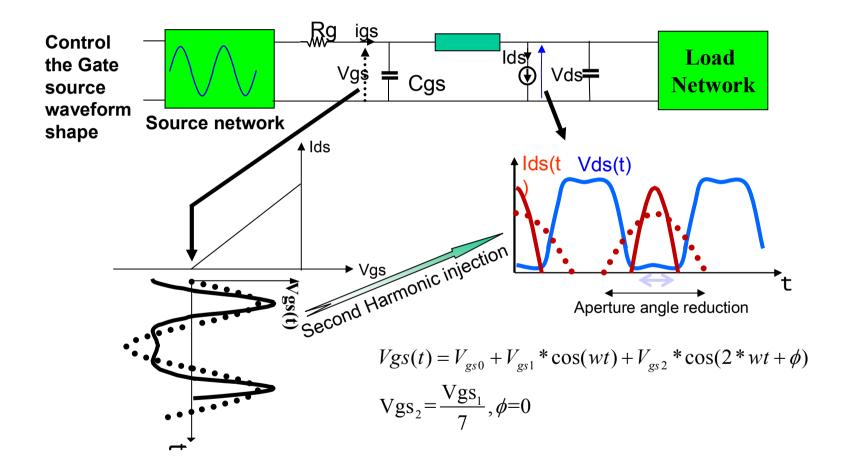

# Waveform engineering to increase PAE

# Simplified GaN HEMT model

#### **➤ Minimization of dissipated power:**

During ON state Vds, must be minimum => Low  $R_{ds,on}$ During transitions  $dV_{ds}/dt$  and  $dI_{ds}/dt$  must be maximum => Low capacitances (Cgs,Cds)

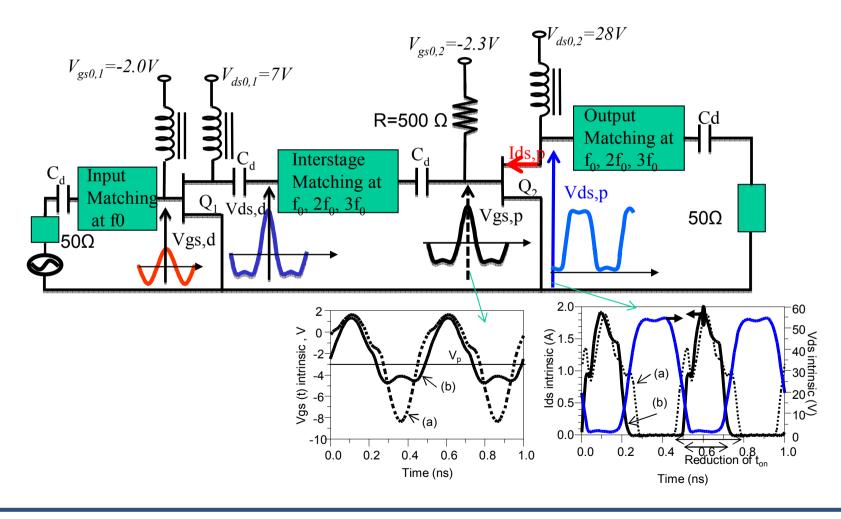

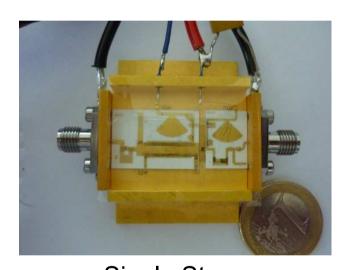

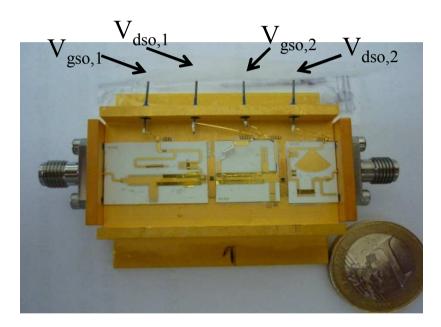

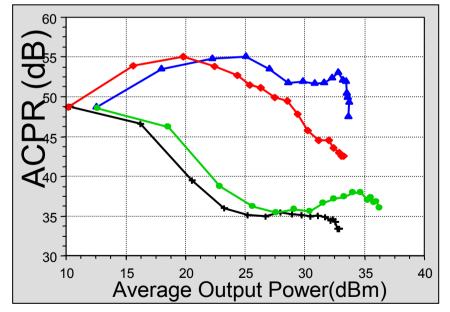

# Two stage PA design

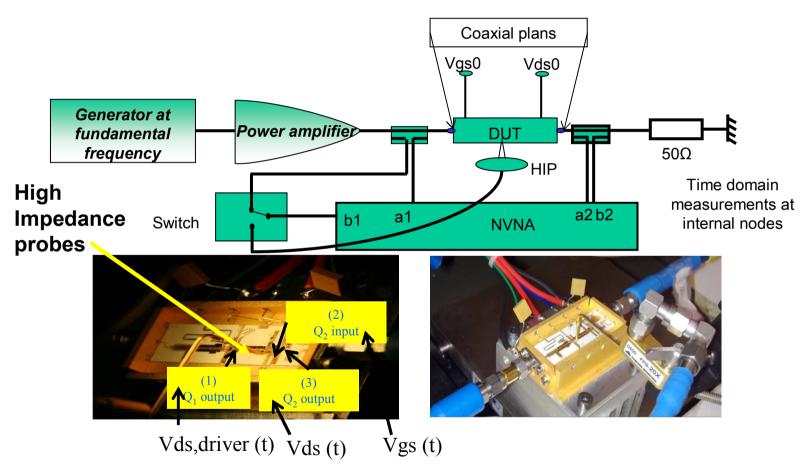

# Time domain measurements at internal nodes

High impedance probing for waveform checking and tuning

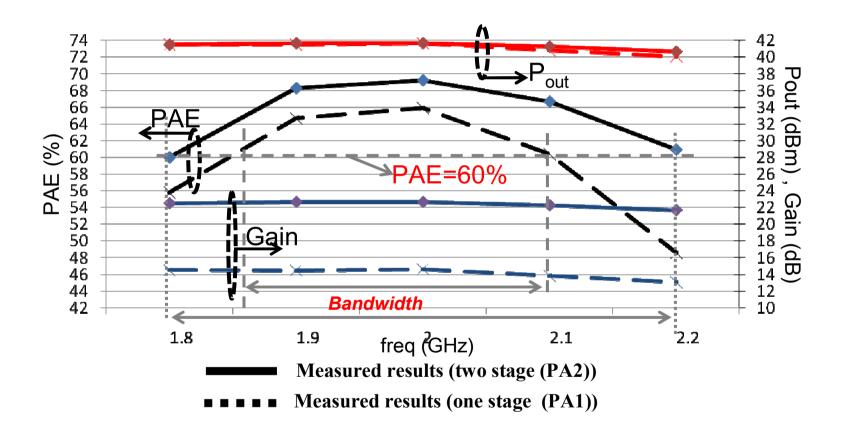

# Comparison with a conventional class F design

Single Stage conventional class F PA (PA1)

Two Stage PA with gate source voltage waveform shaping (PA2)

# Measurement results at connector ports

Comparison between single and two stage Power Amplifiers (same foundry)

Large Signal Measurement results at 4 dB gain compression

#### **Outline**

- Introduction

- Quick overview of classical measurement techniques for NL devices

- Memory effects characterization and modeling

- Waveform engineering based on measurements

- Envelope tracking dynamical biasing / pre-distortion

- High impedance probing

- Conclusion

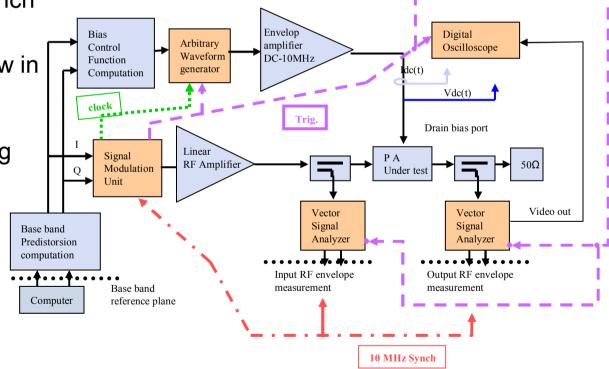

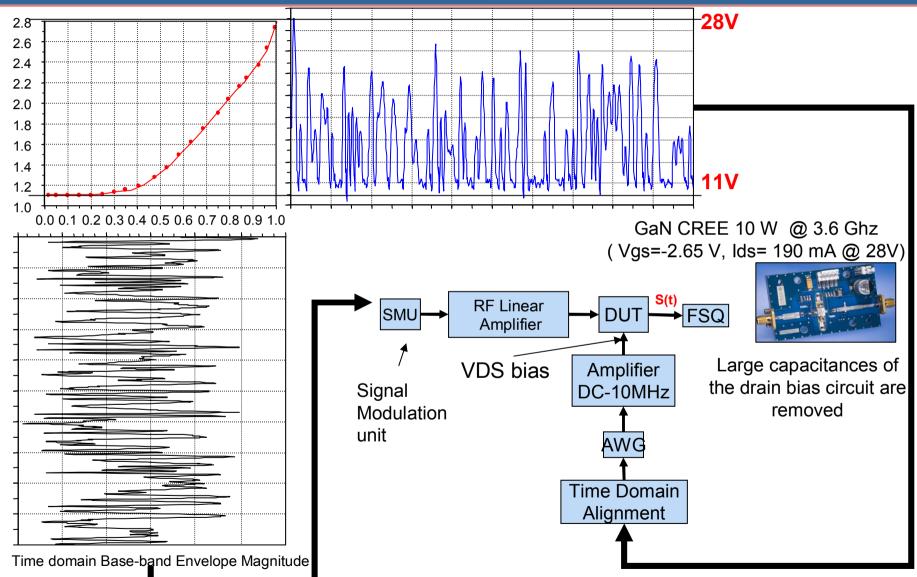

## Smart power amplifier measurement system

High Efficiency ⇒ Power amplifier architectures based on dynamic biasing techniques

Linearity ⇒ Power amplifier architectures based on digital pre-distortion

→ Development of Specific test-Bench

• Identify dynamic drain bias law in presence of memory effects.

Apply both Envelope Tracking (ET) and Digital Pre-Distortion (DPD) techniques.

Maximize both PAE and linearity.

Clock synchronization and envelope trigger signals are carefully controlled Appropriate time alignment between RF signal envelope and drain bias signal are achieved

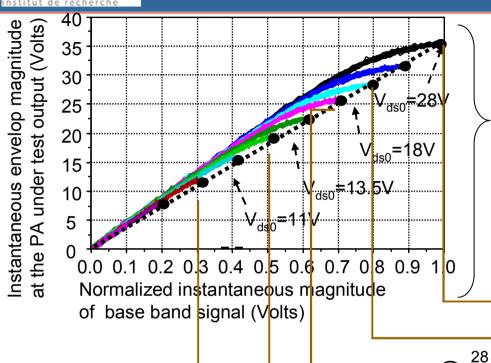

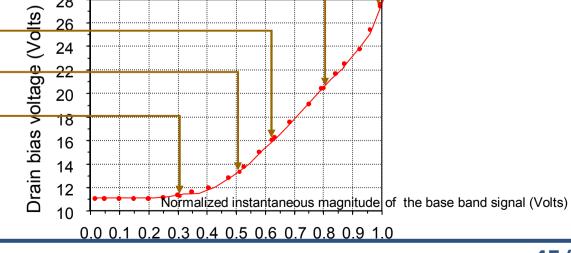

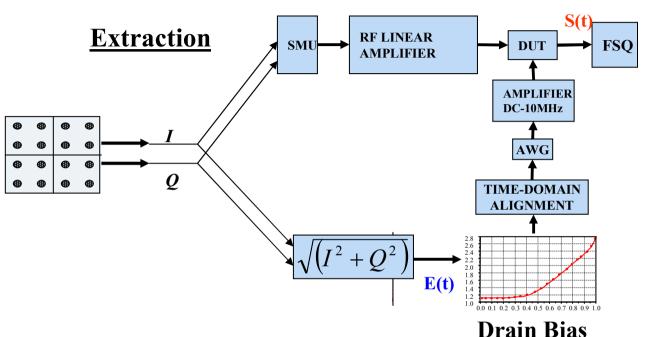

## Extraction of drain bias law (100 KHz 16-QAM)

- ➤ Modulated signal is applied to the PA input (QAM16 in the present case).

- Fixed DC voltage is applied to the drain bias port.

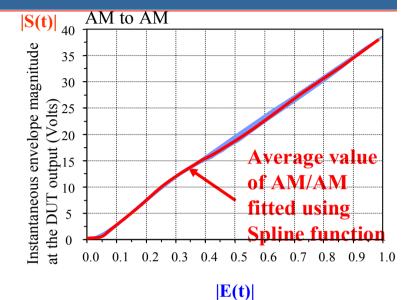

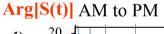

- ➤ Instantaneous input/ output envelop transfer functions are recorded.

The coordinates of the targeted drain bias law are taken to keep constant saturated gain and high drain efficiency

# Application of drain bias law (100 KHz 16-QAM)

# Base-band pre-distortion applied to Envelope Tracking PA

Law

Vienna, April 18th-19th, 2011

- > A simple first order base band predistorsion technique

- ➤ It consists in extracting spline functions fitting the average of measured dynamic AM/AM and AM/PM characteristics of the ET amplifier, and inverting them

- > Can be improved (DSP, FPGA) to consider LF memories

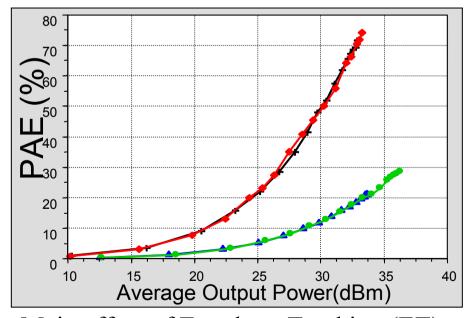

#### Measurement results and comparison

# OFDM Signal 128 sub carriers 16QAM at 1MBit/S Oversampling Ratio=4 Fe=4MHz

GaN CREE 10 W @ 3.6 Ghz (Vgs0=-2.65 V, IdsQ= 190 mA @ 28V)

Main effect of Envelope Tracking (ET)

Main effect of Digital PreDistortion (DPD)

#### **Outline**

- Introduction

- Quick overview of classical measurement techniques for NL devices

- Memory effects characterization and modeling

- Waveform engineering based on measurements

- Envelope tracking dynamical biasing / pre-distortion

- High impedance probing

- Conclusion

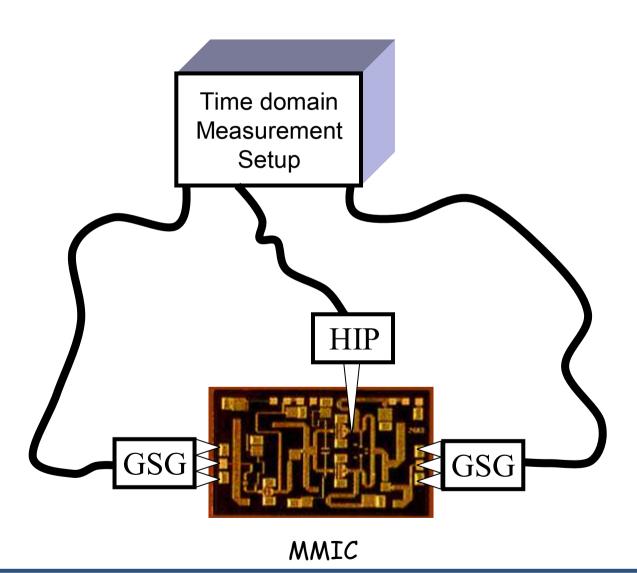

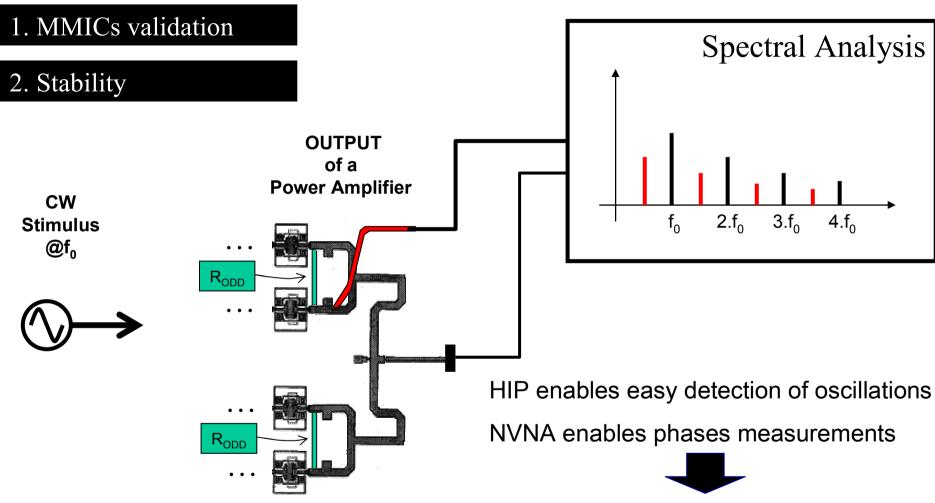

# Motivations for High Impedance Probes (HIP)

# Test-set configuration and matrix

# HIP calibration assumption

$$V_{\text{ref.plane}}(f) = \widetilde{K}(f).V_{\text{raw}}(f)$$

## HIP calibration tips

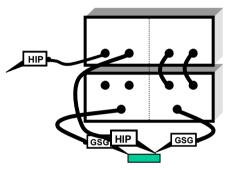

# 1. NVNA calibration (LRRM)

# GSG GSG

$$\begin{pmatrix} vl \\ il \\ v2 \\ i2 \end{pmatrix}_{LSNA} = \begin{bmatrix} \alpha_1 & \beta_1 & 0 & 0 \\ \gamma_1 & \delta_1 & 0 & 0 \\ 0 & 0 & \alpha_2 & \beta_2 \\ 0 & 0 & \gamma_2 & \delta_2 \end{bmatrix} \bullet \begin{pmatrix} rl \\ r2 \\ r3 \\ r4 \end{pmatrix}_{LSNA}$$

→ Ref. plane = voltage standard

# 2. Calibration with 1 HIP

$\rightarrow$   $\widetilde{K}(f) = \frac{v_2(f)}{v_{HIP}(f)}$

- HIP @ ref. plane

- « Sweep-sin »

- Measurements:

- > V<sub>2</sub> (NVNA calibrated)

- > V<sub>HIP</sub> (raw data)

# 3. Define a new error-matrix (NVNA + 2 HIPs)

# Measurement of 2 voltages (M1)

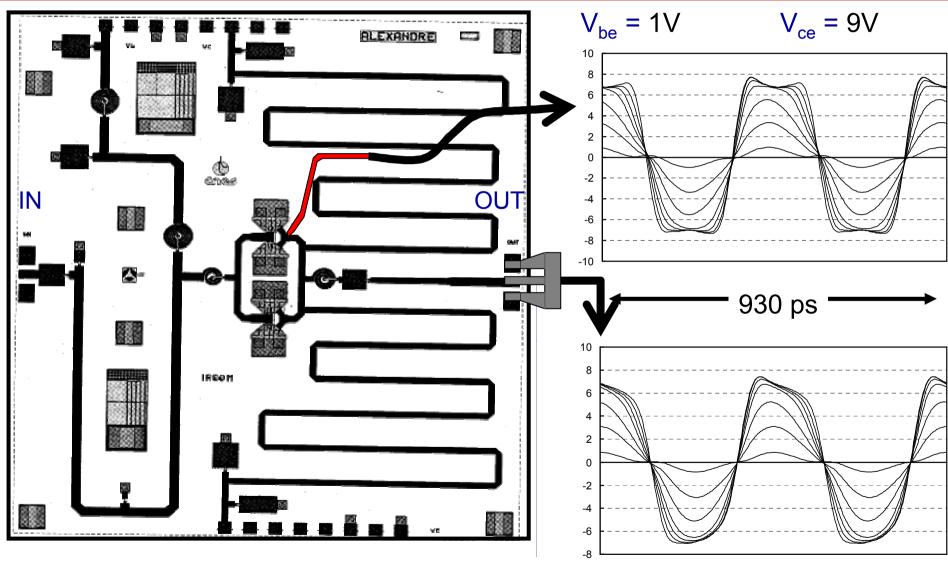

# HIP measurement applications (1/2)

# HIP measurement applications (2/2)

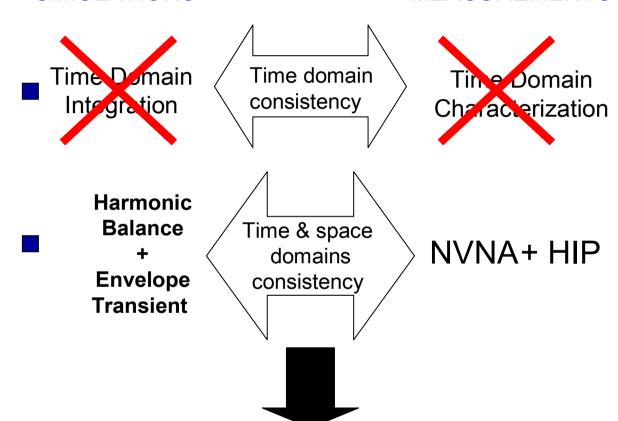

KNOWLEDGE OF NONLINEAR PHENOMENA OPTIMAL DESIGN FOR POWER AMPLIFIERS

## HIP + NVNA open the way to measurementbased waveform engineering of SSPAs

#### **SIMULATIONS**

#### **MEASUREMENTS**

Analysis...

Identification...

Understanding...

of

DYNAMICS NONLINEAR PHENOMENA

Optimized designs of MMICs

#### **Outline**

- Introduction

- Quick overview of classical measurement techniques for NL devices

- Memory effects characterization and modeling

- Waveform engineering based on measurements

- Envelope tracking dynamical biasing / pre-distortion

- High impedance probing

- Conclusion

#### **Conclusions**

- NonLinear measurement of RF active devices are mandatory

- for transistor test, modeling and model verifications

- for memory effects identification

- for direct optimization of SSPAs

- for reliability investigations

-

- Research is still going on

- New ways to separate and accurately measure LF memories

- New measurement instruments, new set-ups

- Cost of NL measurements is to be considered (Return On Invest)

- We estimate that clever NL meas. are the best way for SSPA 1st pass success

A lot of research on RF NL topics (measurement, modeling, instrumentation...) is carried out in Europe. Here in Vienna it's the good place to thank again the TARGET Network of Excellence for its unvaluable support.